MAX16051ETI 데이터 시트보기 (PDF) - Maxim Integrated

부품명

상세내역

제조사

MAX16051ETI Datasheet PDF : 24 Pages

| |||

MAX16050/MAX16051

Voltage Monitors/Sequencer Circuits with

Reverse-Sequencing Capability

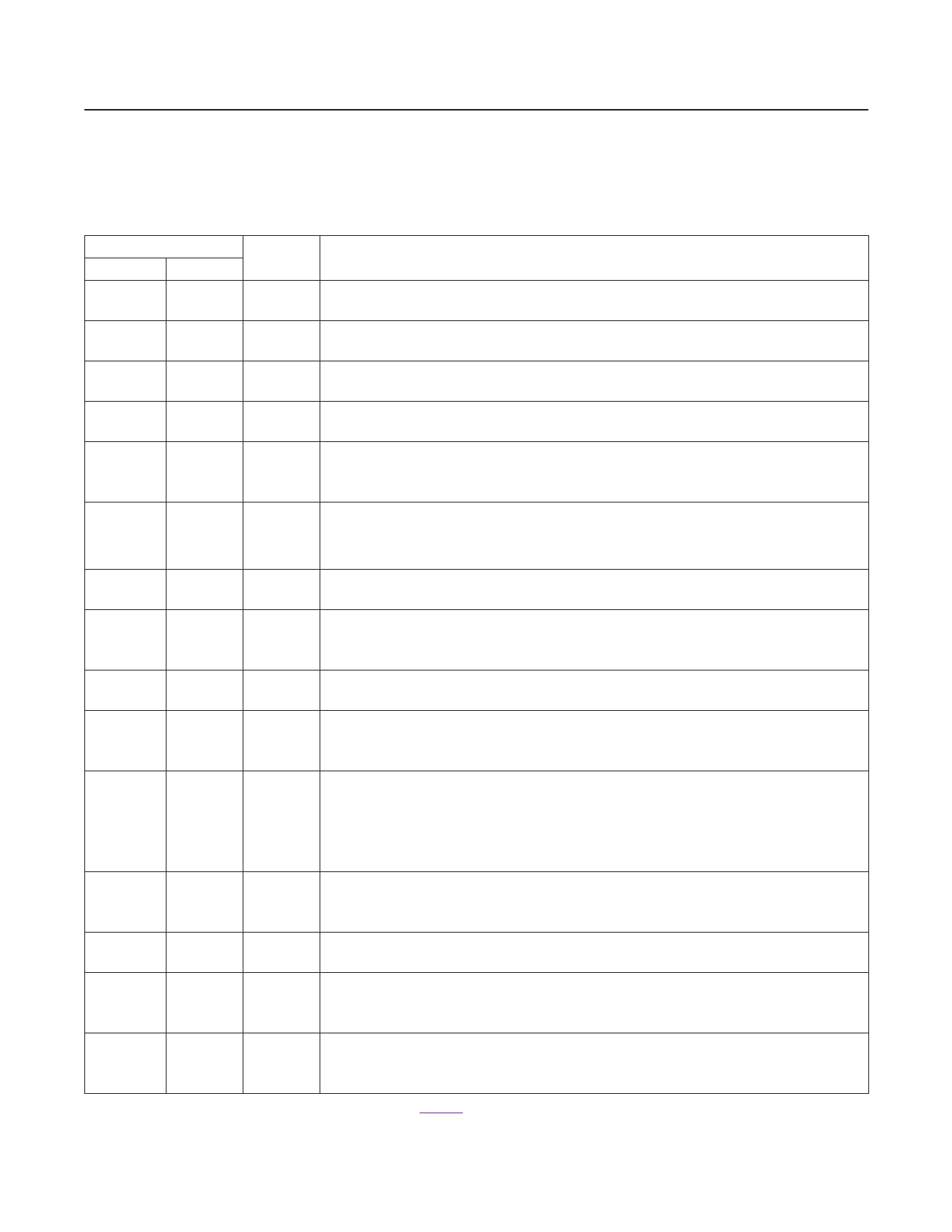

Pin Description (continued)

PIN

MAX16050 MAX16051

10

10

11

11

12

12

13

13

NAME

DISC3

SET2

OUT2

DISC2

FUNCTION

Discharge Pulldown Input 3. During normal operation, DISC3 is high impedance. During a

fault condition or power-down, DISC3 provides an 85mA sink current.

Set Monitored Threshold 2 Input. Monitor a voltage by setting the threshold with an external

resistive divider. The SET2 threshold is 0.5V.

Open-Drain Output 2. When the voltage at SET1* is above 0.5V, OUT2 goes high

impedance. OUT2 requires an external pullup resistor and can be pulled up to VCC.

Discharge Pulldown Input 2. During normal operation, DISC2 is high impedance. During a

fault condition or power-down, DISC2 provides an 85mA sink current.

Enable Hold Input. When EN_HOLD is low, the device does not start the reverse-

14

14

EN_HOLD sequencing process regardless of the status of the SHDN input. Reverse sequencing is

allowed when this input is pulled high. Connect to ABP if unused.

Open-Drain Bus Removal Output. REM goes high impedance when all DISC_ inputs are

15

15

REM below the DISC_ power low threshold (VTH_PL). REM goes low when any DISC_ input

goes above VTH_PL. REM requires an external pullup resistor and can be pulled up to VCC.

16

16

DISC1

Discharge Pulldown Input 1. During normal operation, DISC1 is high impedance. During a

fault condition or power-down, DISC1 provides an 85mA sink current.

Open-Drain Output 1. OUT1 goes high impedance, when the following startup conditions

17

17

OUT1 are met*: VABP > VUVLO, VEN > VTH_EN, SHDN not asserted, and DISC_ voltages

< 250mV. OUT1 requires an external pullup resistor and can be pulled up to VCC.

18

18

SET1

Set Monitored Threshold 1 Input. Monitor a voltage by setting the threshold with an external

resistive divider. The SET1 threshold is 0.5V.

Open-Drain Overvoltage Output. When any of the SET_ voltages exceed their 0.55V

19

19

OV_OUT overvoltage threshold, OV_OUT goes low. When all of the SET_ voltages are below their

overvoltage threshold, OV_OUT goes high impedance after a short propagation delay.

Open-Drain Reset Output. When any of the monitored voltages (including EN) falls below

its threshold, SHDN is pulled low, or FAULT is pulled low, RESET asserts and stays

20

20

RESET asserted for at least the minimum reset timeout period after all of these conditions are

removed. The reset timeout is 128ms (typ) when TIMEOUT is connected to ABP or can be

adjusted by connecting a capacitor from TIMEOUT to GND.

FAULT Synchronization Input/Output. While EN = SHDN = high, FAULT is pulled low when

21

21

FAULT any of the SET_ voltages falls below their respective threshold. Pull FAULT low manually to

assert a simultaneous power-down. FAULT is internally pulled up to ABP by a 100kΩ resistor.

22

22

SHDN

Active-Low Shutdown Input. When SHDN is pulled low, the device will reverse sequence

for power-down operation. SHDN is internally pulled up to ABP by a 100kΩ resistor.

Adjustable Sequence Delay Timing Input. Connect a capacitor from DELAY to GND to

23

23

DELAY set the sequence delay between each OUT_. Leave DELAY unconnected for a 10µs (typ)

delay. The capacitor-adjusted delay occurs on power-up, not on power down.

Adjustable Reset Timeout Input. Connect a capacitor from TIMEOUT to GND to set the

24

24

TIMEOUT reset timeout period. Connect TIMEOUT to ABP for the fixed timeout of 128ms (typ). Leave

TIMEOUT unconnected for a 10µs (typ) delay.

*This applies to the MAX16051. For the MAX16050, see Table 1 for the output sequence order.

www.maximintegrated.com

Maxim Integrated │ 8