AS3909 데이터 시트보기 (PDF) - austriamicrosystems AG

부품명

상세내역

제조사

AS3909 Datasheet PDF : 77 Pages

| |||

Application Information

FIFO Water Level and FIFO Status Register

The AS3909/10 contains a 32 byte FIFO. In case of transmitting

the Control logic shifts data which was previously loaded by the

external microcontroller to the Framing Block and further to the

Transmitter. During reception, the demodulated data is stored

in the FIFO and the external microcontroller can download

received data once reception was terminated.

Transmit and receive capability the AS3909/10 is not limited by

of the FIFO size due to a FIFO water level interrupt system.

During transmission an interrupt is sent (interrupt due to FIFO

water level) when the content of data in the FIFO which still

need to be sent is lower than the FIFO water level for receive.

The external microcontroller can now add more data in the FIFO.

The same stands for receive mode. In case the number of

received bytes gets over the FIFO water level for receive an

interrupt is sent to inform the external controller that data has

to be downloaded from FIFO.

The external controller has to serve the FIFO faster than data is

transmitted or received. A general rule is that the SCLK

frequency has to be at least double than the actual data rate in

receive or transmit.

There are two settings of the FIFO water level available for

receive and transmit in Configuration Register 5 (#05).

After data is received the external microcontroller needs to

know how long the receive data string was before downloading

data from the FIFO: This information is available in the FIFO

Status Register (#09) which displays number of bytes in the FIFO

which were not read out.

The FIFO Status Register also contains a FIFO overflow bit. This

bit is set when during reception the external processor did not

react on time and more than 32 bytes were written in FIFO. The

received data is of course lost in such a case.

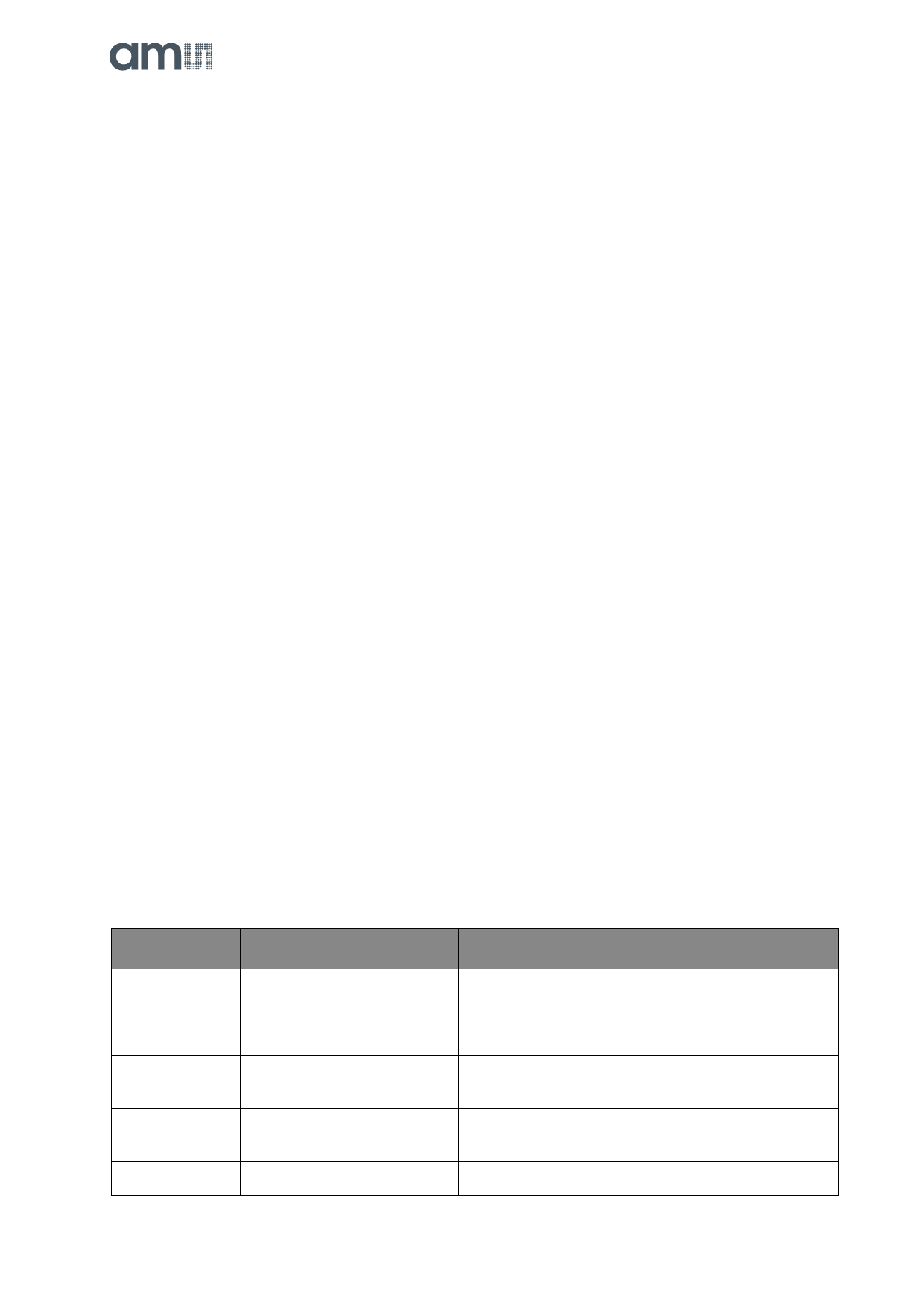

Figure 20:

List of Direct Commands

Direct Commands

Code

000001

000010

000100

000101

000110

Command

Set default

Clear

Transmit with CRC

Transmit without CRC

Transmit REQA

Comments

Puts the AS3909/10 in default state (same as after

power-up)

Stops all activities and clears FIFO

Starts a transmit sequence using automatic CRC

generation

Starts a transmit sequence without automatic CRC

generation

Transmits REQA command (ISO-14443A mode only)

AS3909/AS3910 – 28

ams Datasheet, Confidential: 2013-Oct [3-02]