AT90S8515 데이터 시트보기 (PDF) - Atmel Corporation

부품명

상세내역

제조사

AT90S8515 Datasheet PDF : 112 Pages

| |||

AT90S8515

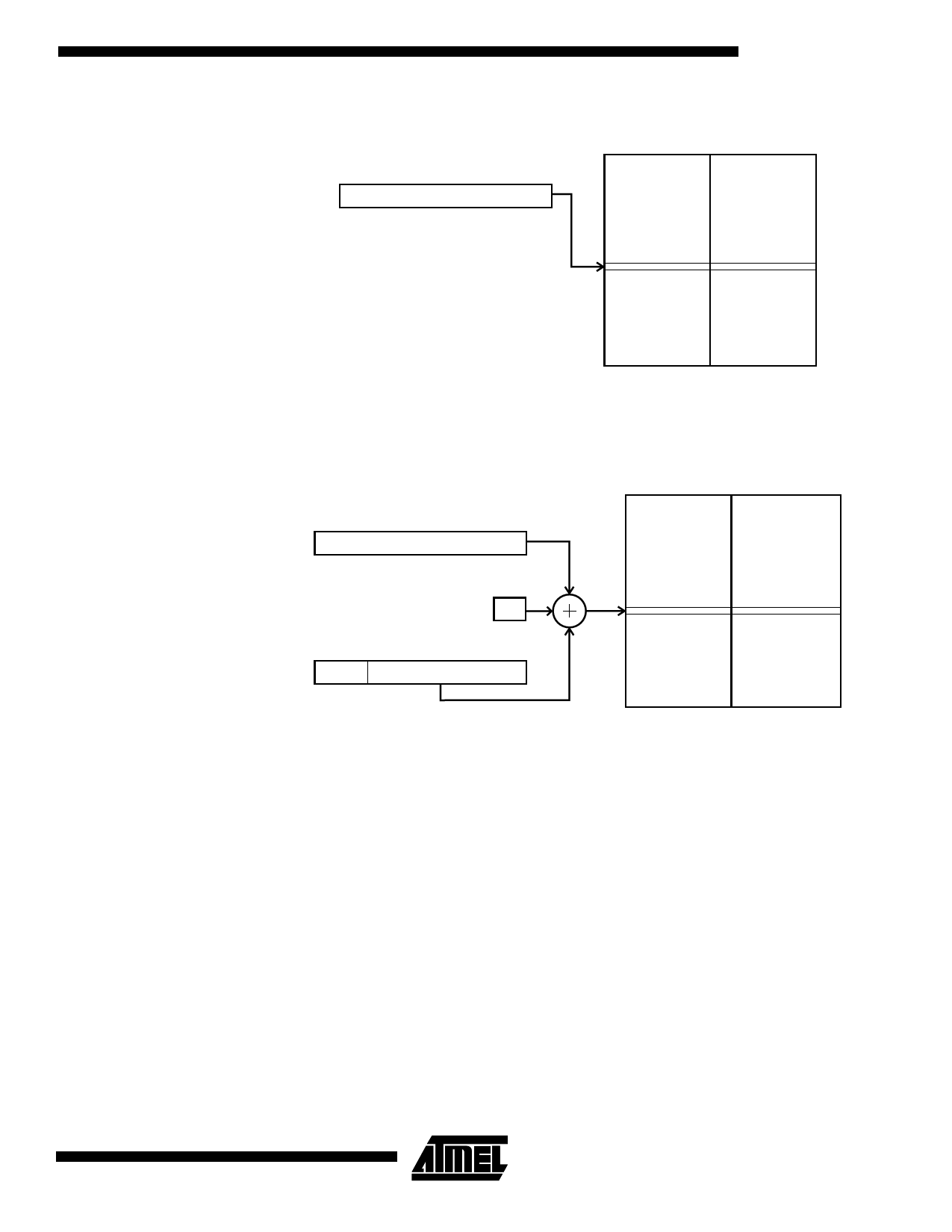

Indirect Program Addressing, Figure 18. Indirect Program Memory Addressing

IJMP and ICALL

PROGRAM MEMORY

$000

15

0

Z-REGISTER

$FFF

Program execution continues at address contained by the Z-register (i.e., the PC is

loaded with the contents of the Z-register).

Relative Program Addressing, Figure 19. Relative Program Memory Addressing

RJMP and RCALL

PROGRAM MEMORY

$000

15

0

PC

EEPROM Data Memory

Memory Access Times

and Instruction

Execution Timing

+1

15 12 11

0

OP

k

$FFF

Program execution continues at address PC + k + 1. The relative address k is -2048 to

2047.

The AT90S8515 contains 512 bytes of data EEPROM memory. It is organized as a sep-

arate data space, in which single bytes can be read and written. The EEPROM has an

endurance of at least 100,000 write/erase cycles. The access between the EEPROM

and the CPU is described on page 44, specifying the EEPROM address registers, the

EEPROM data register and the EEPROM control register.

For the SPI data downloading, see page 86 for a detailed description.

This section describes the general access timing concepts for instruction execution and

internal memory access.

The AVR CPU is driven by the System Clock Ø, directly generated from the external

clock crystal for the chip. No internal clock division is used.

Figure 20 shows the parallel instruction fetches and instruction executions enabled by

the Harvard architecture and the fast-access register file concept. This is the basic pipe-

lining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for

functions per cost, functions per clocks and functions per power unit.

17

0841G–09/01