A80960CF-40 데이터 시트보기 (PDF) - Intel

부품명

상세내역

제조사

A80960CF-40 Datasheet PDF : 77 Pages

| |||

A

80960CF-40, -33, -25, -16

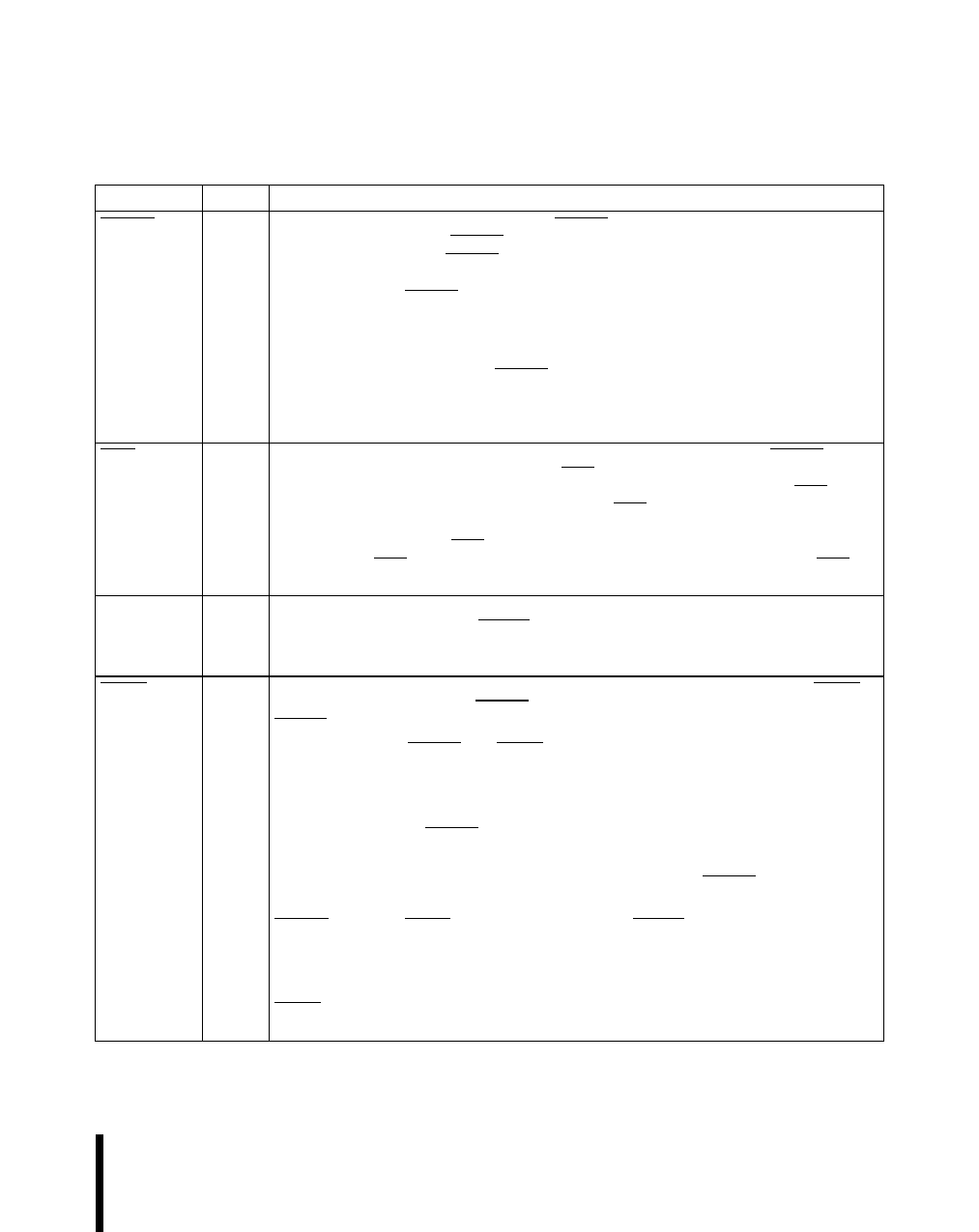

Table 3. 80960CF Pin Description — Processor Control Signals (Sheet 1 of 2)

Name

RESET

FAIL

STEST

ONCE

Type

I

A(L)

H(Z)

R(Z)

O

S

H(Q)

R(0)

I

S(L)

H(Z)

R(Z)

I

A(L)

H(Z)

R(Z)

Description

RESET causes the chip to reset. When RESET is asserted, all external signals return

to the reset state. When RESET is deasserted, initialization begins. When the 2-x

clock mode is selected, RESET must remain asserted for 32 CLKIN cycles before

being deasserted to guarantee correct processor initialization. When the 1-x clock

mode is selected, RESET must remain asserted for 10,000 CLKIN cycles before

being deasserted to guarantee correct processor initialization. The CLKMODE pin

selects 1-x or 2-x input clock division of the CLKIN pin.

The Hold Acknowledge bus state functions while the chip is reset. If the bus is in the

Hold Acknowledge state when RESET is asserted, the processor internally resets,

but maintains the Hold Acknowledge state on external pins until the Hold request is

removed. If a Hold request is made while the processor is in the reset state, the

processor bus grants HOLDA and enters the Hold Acknowledge state.

FAIL indicates failure of the self-test performed at initialization. When RESET is

deasserted and initialization begins, the FAIL pin is asserted. An internal self-test is

performed as part of the initialization process. If this self-test passes, the FAIL pin is

deasserted; otherwise it remains asserted. The FAIL pin is reasserted while the

processor performs an external bus self-confidence test. If this self-test passes, the

processor deasserts the FAIL pin and branches to the user’s initialization routine;

otherwise the FAIL pin remains asserted. Internal self-test and the use of the FAIL pin

can be disabled with the STEST pin.

SELF TEST enables or disables the internal self-test feature at initialization. STEST

is read on the rising edge of RESET. When asserted, internal self-test and external

bus confidence tests are performed during processor initialization. When deasserted,

only the bus confidence tests are performed during initialization.

ON CIRCUIT EMULATION, when asserted, causes all outputs to be floated. ONCE is

continuously sampled while RESET is low and is latched on the rising edge of

RESET. To place the processor in the ONCE state:

(1)

assert RESET and ONCE (order does not matter)

(2)

wait for at least 16 CLKIN periods in 2-x mode—or 10,000 CLKIN

periods in 1-x mode—after VCC and CLKIN are within operating

specifications

(3)

deassert RESET

(4)

wait at least 32 CLKIN periods

(The processor will now be latched in the ONCE state while RESET is high.)

To exit the ONCE state, bring VCC and CLKIN to operating conditions, then assert

RESET and bring ONCE high prior to deasserting RESET.

CLKIN must operate within the specified operating conditions until Step 4 completes.

CLKIN may then be changed to DC to achieve the lowest possible ONCE mode

leakage current.

ONCE can be used by emulator products or board testers to effectively make an

installed processor transparent in the board.

PRELIMINARY

9