IS61VPD51232-166TQI 데이터 시트보기 (PDF) - Integrated Silicon Solution

부품명

상세내역

제조사

IS61VPD51232-166TQI

IS61VPD51232-166TQI Datasheet PDF : 24 Pages

| |||

IS61VPD51232 IS61VPD51236 IS61VPD10018

ISSI ®

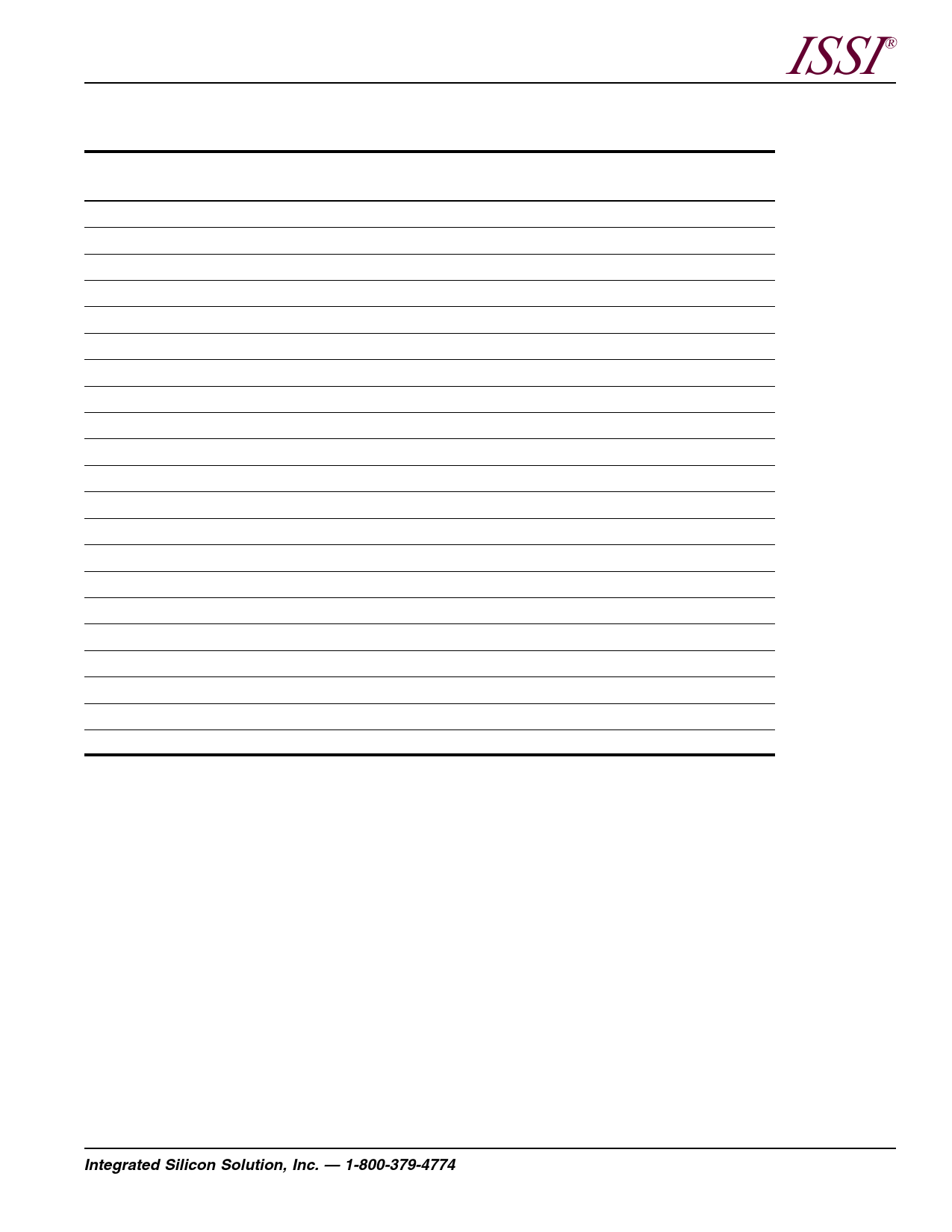

READ/WRITE CYCLE SWITCHING CHARACTERISTICS (Over Operating Range)

Symbol Parameter

-200

Min. Max.

-166

Min. Max.

Unit

fMAX Clock Frequency

—

200

—

166

MHz

tKC

Cycle Time

5

—

6

—

ns

tKH

Clock High Pulse Width

2

—

2.3

—

ns

tKL

Clock Low Pulse Width

2

—

2.3

—

ns

tKQ

Clock Access Time

—

3.1

—

3.5

ns

tKQX(1) Clock High to Output Invalid

1.0

—

1.5

—

ns

tKQLZ(1,2) Clock High to Output Low-Z

0

—

0

—

ns

tKQHZ(1,2) Clock High to Output High-Z

—

3.1

—

3.5

ns

tOEQ Output Enable to Output Valid

—

3.1

—

3.5

ns

tOELZ(1,2) Output Enable to Output Low-Z

0

—

0

—

ns

tOEHZ(1,2) Output Enable to Output High-Z

—

3.0

—

3.2

ns

tAS

Address Setup Time

1.5

—

1.5

—

ns

tSS

Address Status Setup Time

1.5

—

1.5

—

ns

tWS Write Setup Time

1.5

—

1.5

—

ns

tCES Chip Enable Setup Time

1.5

—

1.5

—

ns

tAVS Address Advance Setup Time

1.5

—

1.5

—

ns

tAH

Address Hold Time

0.5

—

0.5

—

ns

tSH

Address Status Hold Time

0.5

—

0.5

—

ns

tWH Write Hold Time

0.5

—

0.5

—

ns

tCEH Chip Enable Hold Time

0.5

—

0.5

—

ns

tAVH Address Advance Hold Time

0.5

—

0.5

—

ns

Note:

1. Guaranteed but not 100% tested. This parameter is periodically sampled.

2. Tested with load in Figure 2.

Integrated Silicon Solution, Inc. — 1-800-379-4774

11

ADVANCE INFORMATION Rev. 00B

09/25/01