M50FW040K5P 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

제조사

M50FW040K5P Datasheet PDF : 53 Pages

| |||

M50FW040

Bus operations

Table 5. FWH bus Write field definitions

Clock Clock

Cycle Cycle Field

Number Count

FWH0- Memory

FWH3 I/O

Description

On the rising edge of CLK with FWH4 Low, the

1

1 START 1110b

I contents of FWH0-FWH3 indicate the start of a

FWH Write Cycle.

Indicates which FWH Flash Memory is selected.

The value on FWH0-FWH3 is compared to the

2

1 IDSEL XXXX

I IDSEL strapping on the FWH Flash Memory pins to

select which FWH Flash Memory is being

addressed.

3-9

7 ADDR XXXX

I

A 28-bit address phase is transferred starting with

the most significant nibble first.

10

1 MSIZE 0000b

I Always 0000b (single byte transfer).

11-12

2 DATA XXXX

I

Data transfer is two cycles, starting with the least

significant nibble.

13

1 TAR 1111b

I

The host drives FWH0-FWH3 to 1111b to indicate

a turnaround cycle.

14

1

TAR

1111b

(float)

O

The FWH Flash Memory takes control of FWH0-

FWH3 during this cycle.

The FWH Flash Memory drives FWH0-FWH3 to

15

1 SYNC 0000b

O 0000b, indicating it has received data or a

command.

16

1 TAR 1111b

O

The FWH Flash Memory drives FWH0-FWH3 to

1111b, indicating a turnaround cycle.

17

1

TAR

1111b

(float)

N/A

The FWH Flash Memory floats its outputs and the

host takes control of FWH0-FWH3.

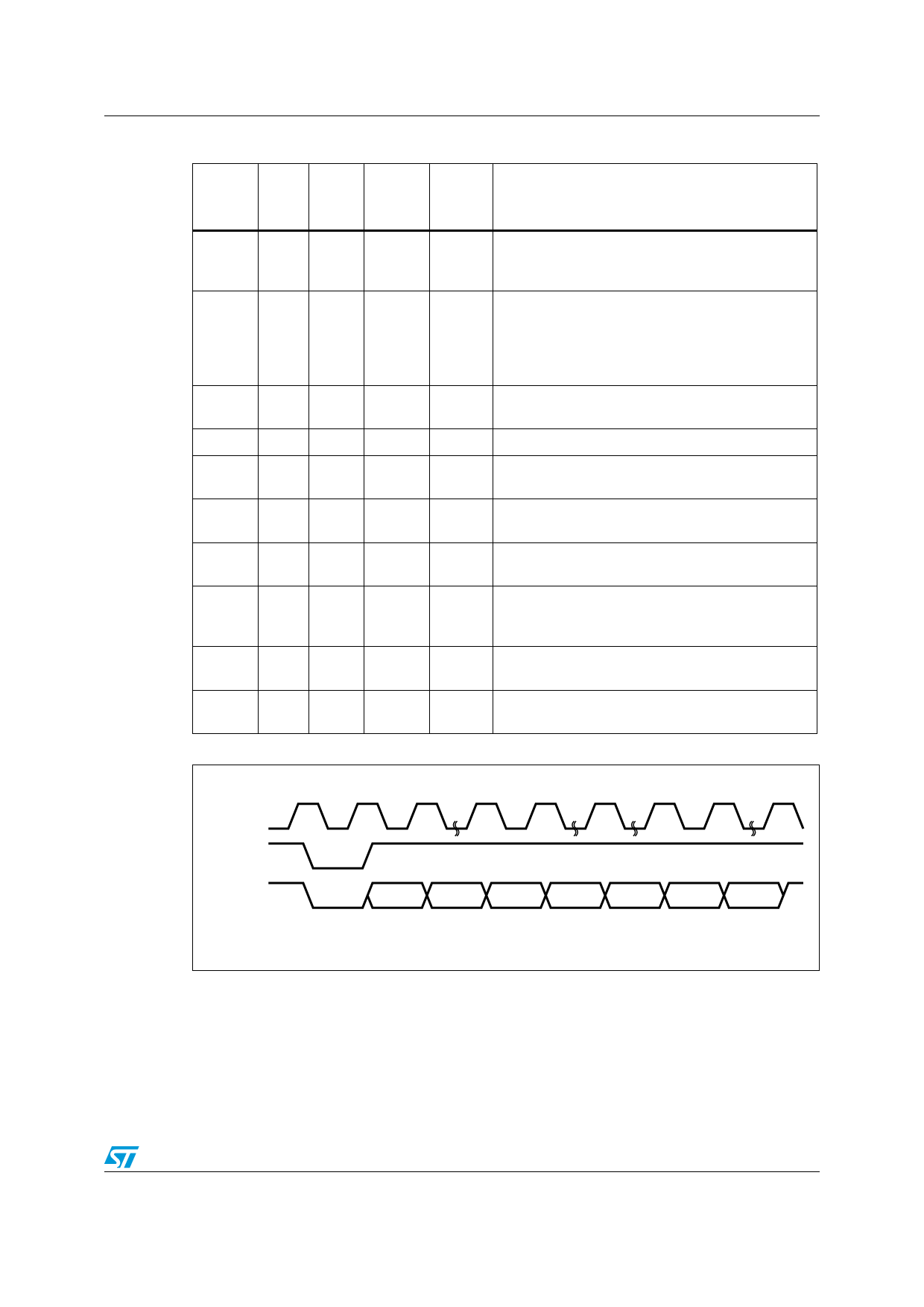

Figure 7. FWH Bus Write waveforms

CLK

FWH4

FWH0-FWH3

Number of

clock cycles

START

1

IDSEL

1

ADDR

7

MSIZE

1

DATA

2

TAR

2

SYNC

1

TAR

2

AI03441

21/53