MFRC523 데이터 시트보기 (PDF) - NXP Semiconductors.

부품명

상세내역

제조사

MFRC523 Datasheet PDF : 98 Pages

| |||

NXP Semiconductors

MFRC523

Contactless reader IC

Table 14. Address byte 0 register; address MOSI

7 (MSB) 6

5

4

3

2

1

0 (LSB)

1 = read reserved address

0 = write

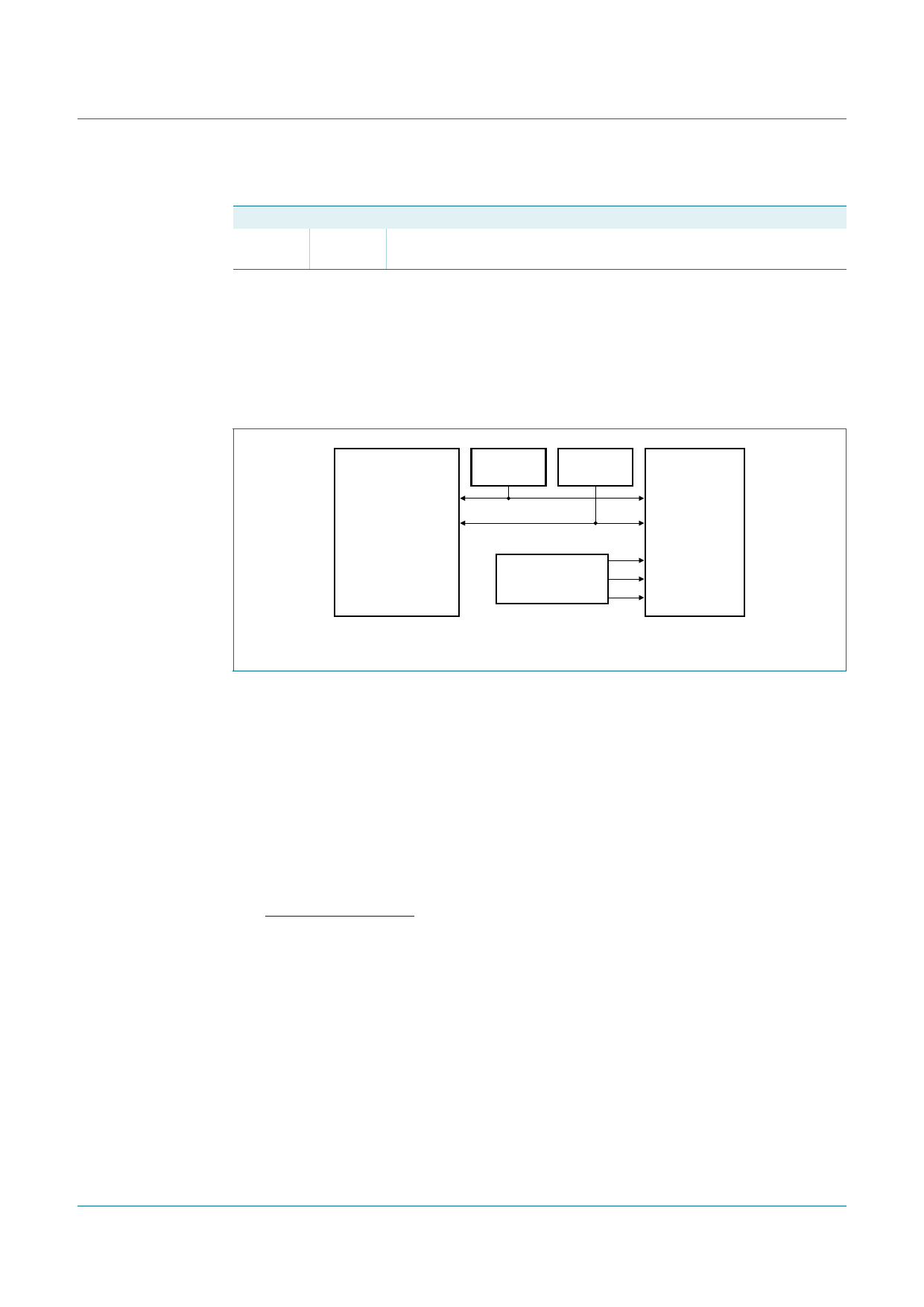

8.3.4 I2C Bus Interface

An I2C-bus (Inter-IC) interface is supported to enable a low-cost, low pin count serial bus

interface to the host. The I2C-bus interface is implemented according to

NXP Semiconductors’ I2C-bus interface specification, rev. 2.1, January 2000. The

interface can only act in Slave mode. Therefore the MFRC523 does not implement clock

generation or access arbitration.

MICROCONTROLLER

Fig 11. I2C-bus interface

PULL-UP

NETWORK

PULL-UP

NETWORK

MFRC523

SDA

SCL

CONFIGURATION

WIRING

I2C

EA

ADR_[5:0]

001aal160

The MFRC523 can act either as a slave receiver or slave transmitter in Standard mode,

Fast mode and High-speed mode.

SDA is a bidirectional line connected to a positive supply voltage using a current source or

a pull-up resistor. Both SDA and SCL lines are set HIGH when data is not transmitted. The

MFRC523 has a 3-state output stage to perform the wired-AND function. Data on the

I2C-bus can be transferred at data rates of up to 100 kBd in Standard mode, up to

400 kBd in Fast mode or up to 3.4 Mbit/s in High-speed mode.

If the I2C-bus interface is selected, spike suppression is activated on lines SCL and SDA

as defined in the I2C-bus interface specification.

See Table 155 on page 77 for timing requirements.

MFRC523_33

Product data sheet

PUBLIC

All information provided in this document is subject to legal disclaimers.

Rev. 3.3 — 5 March 2010

115233

© NXP B.V. 2010. All rights reserved.

16 of 98