SAA5233 데이터 시트보기 (PDF) - Philips Electronics

부품명

상세내역

제조사

SAA5233 Datasheet PDF : 20 Pages

| |||

Philips Semiconductors

Dual standard PDC decoder

Objective specification

SAA5233

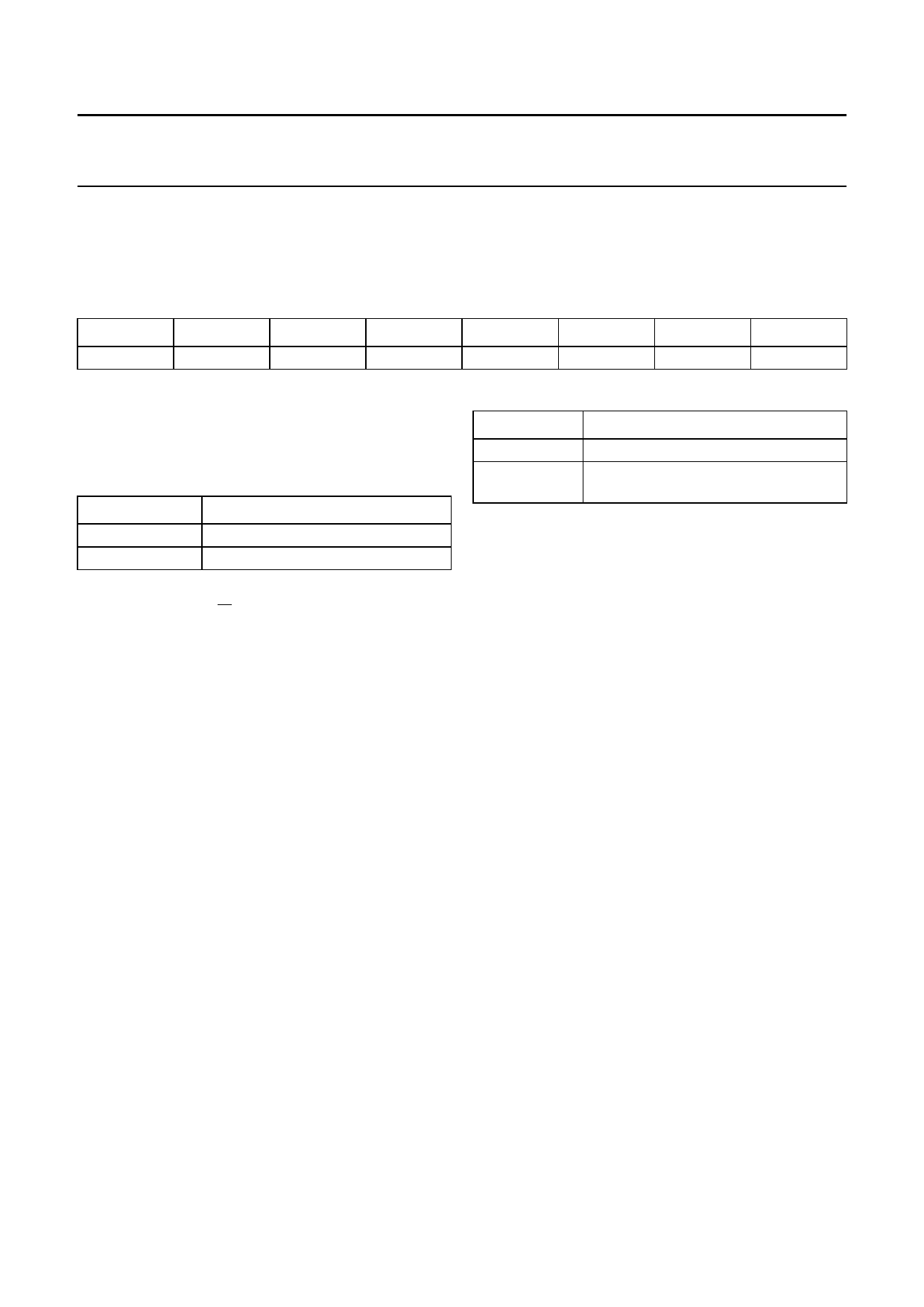

Register 1E to 31D (HEX): Status display message

Data is stored as bytes which represent a Teletext character. The data is odd parity checked, if a parity error occurs this

causes the byte not to be written to the RAM. The MSB is not used and is fixed to logic 0.

Table 14 Register 11.

D7

D6

D5

D4

D3

D2

D1

D0

−

DATA BIT 6 DATA BIT 5 DATA BIT 4 DATA BIT 3 DATA BIT 2 DATA BIT 1 DATA BIT 0

I2C-bus slave address

The slave address for the device can take one of two

values dependent on the state of the input pin AD.

Table 15 Device address.

AD

SLAVE ADDRESS

0

0010 001X(1)

1

0010 000X(1)

Note

1. Where X is the R/W bit.

I2C-bus increment

The I2C-bus will also increment between registers as listed

in Table 16

Table 16 Increment between registers.

ADDRESS

CONTENTS

02 to 0F (HEX) VPS data bytes

11 to 31 (HEX) Teletext packet 8/30/2 data bytes and

Status display message

Addressing any register in either of these ranges will

initialize an increment until the final stop value provided

each byte is acknowledged by the receiver.

Initialization during power-up

The device has an internal power-on reset unit which is

used to reset the I2C-bus interface to be a slave

transceiver. It also initializes the device to receive only

completely valid Teletext packet 8/30/2 and VPS data. The

interrupt signals for both Teletext packet 8/30/2 and VPS

are disabled.

June 1994

14