HMS81004E 데이터 시트보기 (PDF) - Hynix Semiconductor

부품명

상세내역

제조사

HMS81004E Datasheet PDF : 77 Pages

| |||

HMS81004E/08E/16E/24E/32E

[Zero flag Z]

This flag is set when the result of an arithmetic operation

or data transfer is "0" and is cleared by any other result.

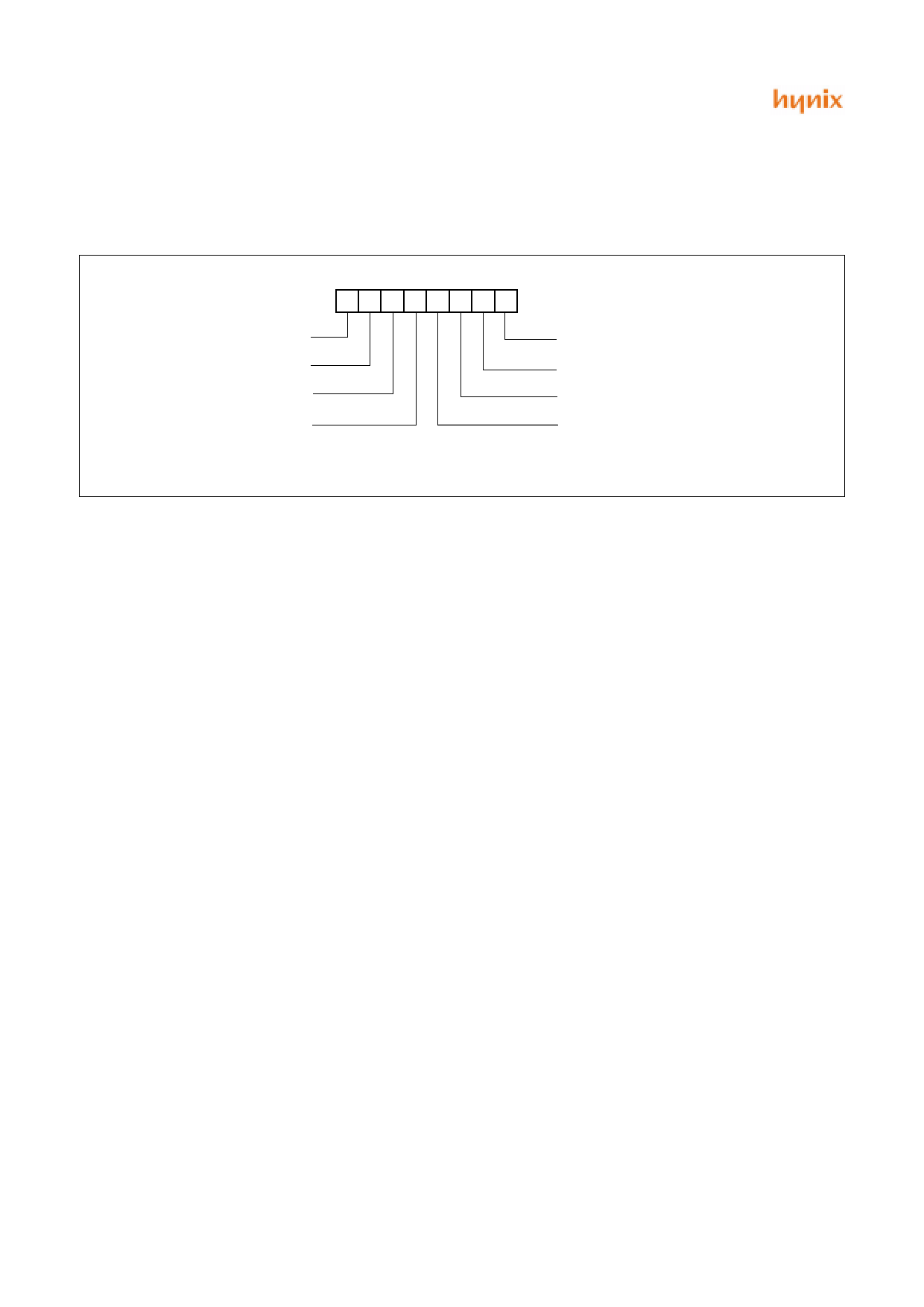

PSW

NEGATIVE FLAG

OVERFLOW FLAG

SELECT DIRECT PAGE

when g=1, page is addressed by RPR

BRK FLAG

MSB

LSB

N V G B H I Z C RESET VALUE : 00H

CARRY FLAG RECEIVES

CARRY OUT

ZERO FLAG

INTERRUPT ENABLE FLAG

HALF CARRY FLAG RECEIVES

CARRY OUT FROM BIT 1 OF

ADDITION OPERLANDS

Figure 8-4 PSW (Program Status Word) Register

[Interrupt disable flag I]

This flag enables/disables all interrupts except interrupt

caused by Reset or software BRK instruction. All inter-

rupts are disabled when cleared to "0". This flag immedi-

ately becomes "0" when an interrupt is served. It is set by

the EI instruction and cleared by the DI instruction.

[Half carry flag H]

After operation, this is set when there is a carry from bit 3

of ALU or there is no borrow from bit 4 of ALU. This bit

can not be set or cleared except CLRV instruction with

Overflow flag (V).

[Break flag B]

This flag is set by software BRK instruction to distinguish

BRK from TCALL instruction with the same vector ad-

dress.

[Direct page flag G]

This flag assigns RAM page for direct addressing mode. In

the direct addressing mode, addressing area is from zero

page 00H to 0FFH when this flag is "0". If it is set to "1",

addressing area is 1 Page. It is set by SETG instruction and

cleared by CLRG.

[Overflow flag V]

This flag is set to "1" when an overflow occurs as the result

of an arithmetic operation involving signs. An overflow

occurs when the result of an addition or subtraction ex-

ceeds +127(7FH) or -128(80H). The CLRV instruction

clears the overflow flag. There is no set instruction. When

the BIT instruction is executed, bit 6 of memory is copied

to this flag.

[Negative flag N]

This flag is set to match the sign bit (bit 7) status of the re-

sult of a data or arithmetic operation. When the BIT in-

struction is executed, bit 7 of memory is copied to this flag.

18

JUNE 2001 Ver 1.00