TDA4857PS 데이터 시트보기 (PDF) - Philips Electronics

부품명

상세내역

제조사

TDA4857PS Datasheet PDF : 56 Pages

| |||

Philips Semiconductors

I2C-bus autosync deflection controller for

PC monitors

Product specification

TDA4857PS

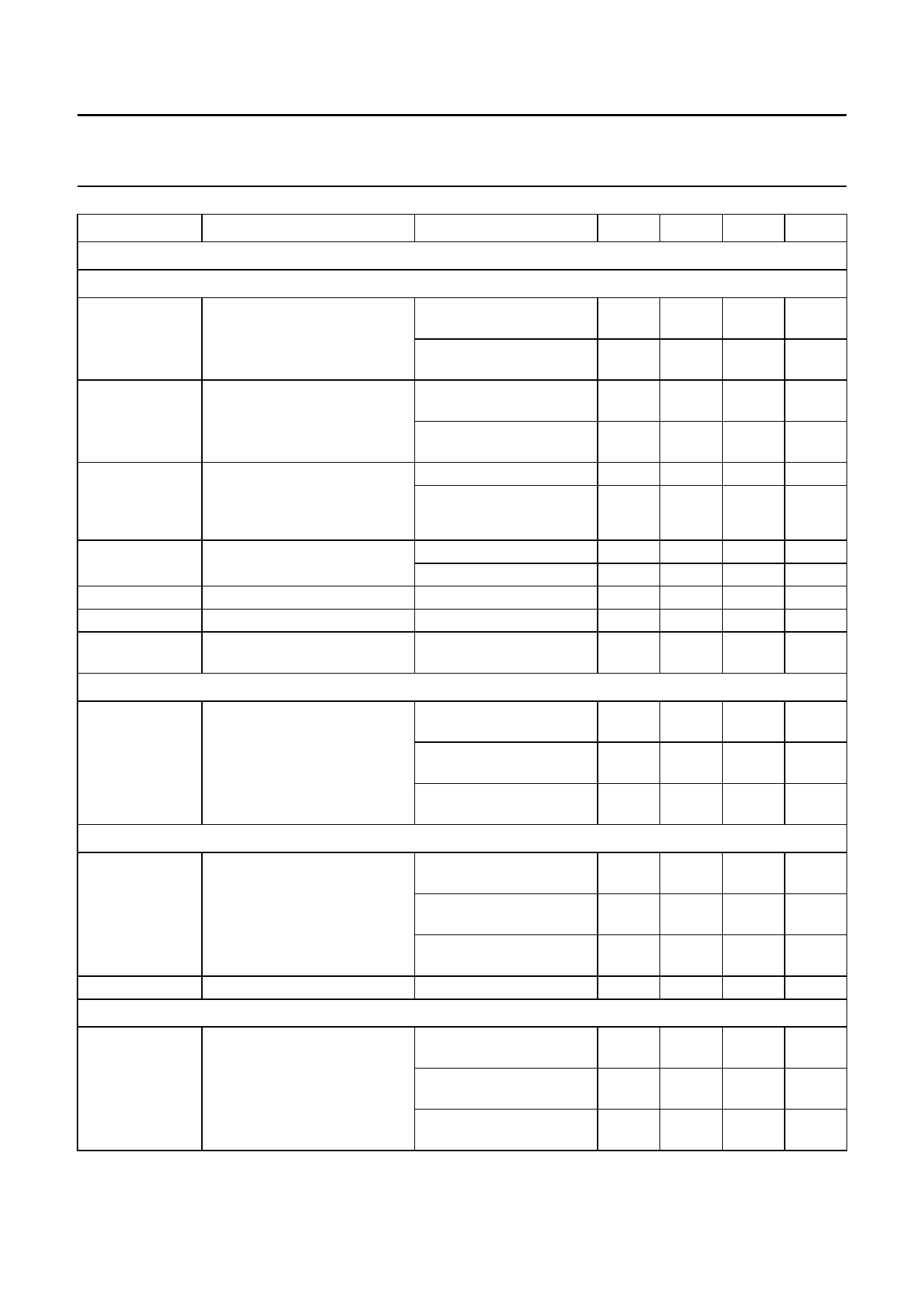

SYMBOL

PARAMETER

CONDITIONS

MIN.

Differential vertical current outputs

ADJUSTMENT OF VERTICAL SIZE INCLUDING VGA AND EHT COMPENSATION; see Fig.3

VSIZE

vertical size without VGA

overscan (referenced to

nominal vertical size)

register VSIZE = 0;

−

bit VOVSCN = 0; note 8

register VSIZE = 127;

−

bit VOVSCN = 0; note 8

VSIZEVGA

vertical size with VGA

overscan (referenced to

nominal vertical size)

register VSIZE = 0;

bit VOVSCN = 1; note 8

register VSIZE = 127;

bit VOVSCN = 1; note 8

−

115.9

VSMODEHT

EHT compensation on vertical IVSMOD = 0

−

size via VSMOD (pin 21)

IVSMOD = −120 µA

−

(referenced to 100% vertical

size)

Ii(VSMOD)

input current (pin 21)

VSMOD = 0

−

VSMOD = −7%

−

Ri(VSMOD)

input resistance

300

Vref(VSMOD)

reference voltage at input

−

fro(VSMOD)

roll-off frequency (−3 dB)

IVSMOD = −60 µA

1

+ 15 µA (RMS)

ADJUSTMENT OF VERTICAL POSITION; see Fig.4

VPOS

vertical position (referenced to register VPOS = 0;

−

100% vertical size)

control bit VPC = 0

register VPOS = 127;

−

control bit VPC = 0

register VPOS = X;

−

control bit VPC = 1

ADJUSTMENT OF VERTICAL LINEARITY; see Fig.5

VLIN

vertical linearity (S-correction) register VLIN = 0;

−

control bit VSC = 0; note 8

register VLIN = 15; control −

bit VSC = 0; note 8

register VLIN = X;

−

control bit VSC = 1; note 8

δVLIN

symmetry error of S-correction maximum VLIN

−

ADJUSTMENT OF VERTICAL LINEARITY BALANCE; see Fig.6

VLINBAL

vertical linearity balance

(referenced to 100% vertical

size)

register VLINBAL = 0;

−3.3

control bit VLC = 0; note 8

register VLINBAL = 15; 1.7

control bit VLC = 0; note 8

register VLINBAL = X;

−

control bit VLC = 1; note 8

TYP.

60

100

70

116.8

0

−7

0

−120

−

5.0

−

−11.5

11.5

0

2

46

0

−

−2.5

2.5

0

MAX. UNIT

−

%

−

%

−

%

117.7 %

−

%

−

%

−

µA

−

µA

500

Ω

−

V

−

MHz

−

%

−

%

−

%

−

%

−

%

−

%

±0.7 %

−1.7 %

3.3

%

−

%

2000 Jan 31

19