CX28HC64DMB-12(2006) 데이터 시트보기 (PDF) - Intersil

부품명

상세내역

제조사

CX28HC64DMB-12 Datasheet PDF : 17 Pages

| |||

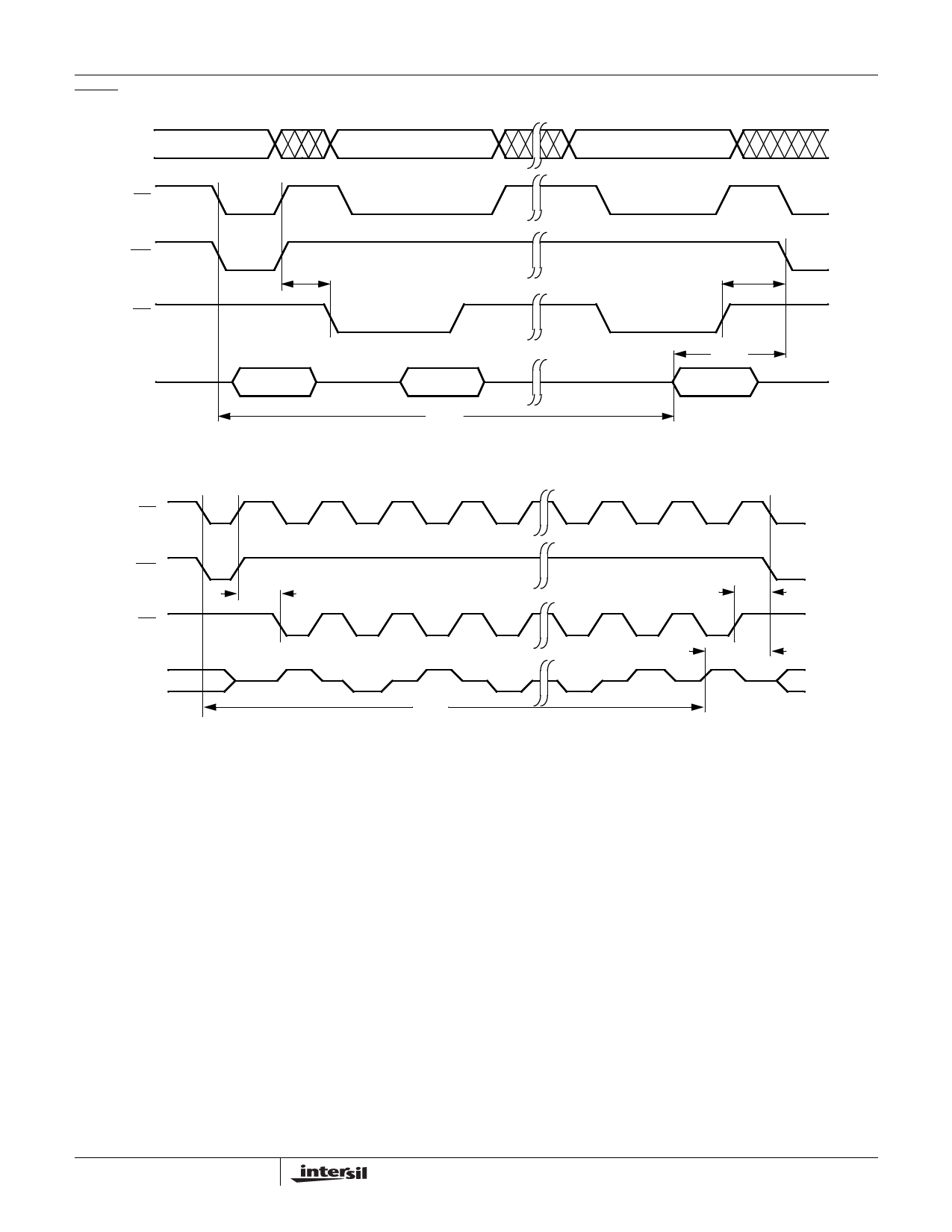

WRITE CYCLE LIMITS

Symbol

tWC(5)

tAS

tAH

tCS

tCH

tCW

tOES

tOEH

tWP

tWPH(6)

tDV(6)

tDS

tDH

tDW(6)

tBLC

Parameter

Write cycle time

Address setup time

Address hold time

Write setup time

Write hold time

CE pulse width

OE High setup time

OE High hold time

WE pulse width

WE HIGH recovery

Data valid

Data setup

Data hold

Delay to next write

Byte load cycle

WE Controlled Write Cycle

Address

CE

tAS

tAH

tCS

X28HC64

Min.

0

50

0

0

50

0

0

50

50

50

0

10

0.15

tWC

tCH

Typ.(1)

2

Max.

5

1

100

Unit

ms

ns

ns

ns

ns

ns

ns

ns

ns

ns

µs

ns

ns

µs

µs

OE

WE

Data In

Data Out

tOES

tDV

tOEH

tWP

Data Valid

tDS

tDH

HIGH Z

Notes: (5) tWC is the minimum cycle time to be allowed from the system perspective unless polling techniques are used. It is the maximum time

the device requires to automatically complete the internal write operation.

(6) tWPH and tDW are periodically sampled and not 100% tested.

15

FN8109.1

June 7, 2006