BT8110 데이터 시트보기 (PDF) - Conexant Systems

부품명

상세내역

제조사

BT8110 Datasheet PDF : 84 Pages

| |||

Bt8110/8110B

High-Capacity ADPCM Processor

Appendix C . E1 Speech Compression

C.1 Introduction

C.1.3 Microprocessor Interface and Per-Channel Configuration

The microprocessor interface of the Bt8510 provides all control and status

functions for the E1 lines; it can also be used to insert and extract signaling in this

application.

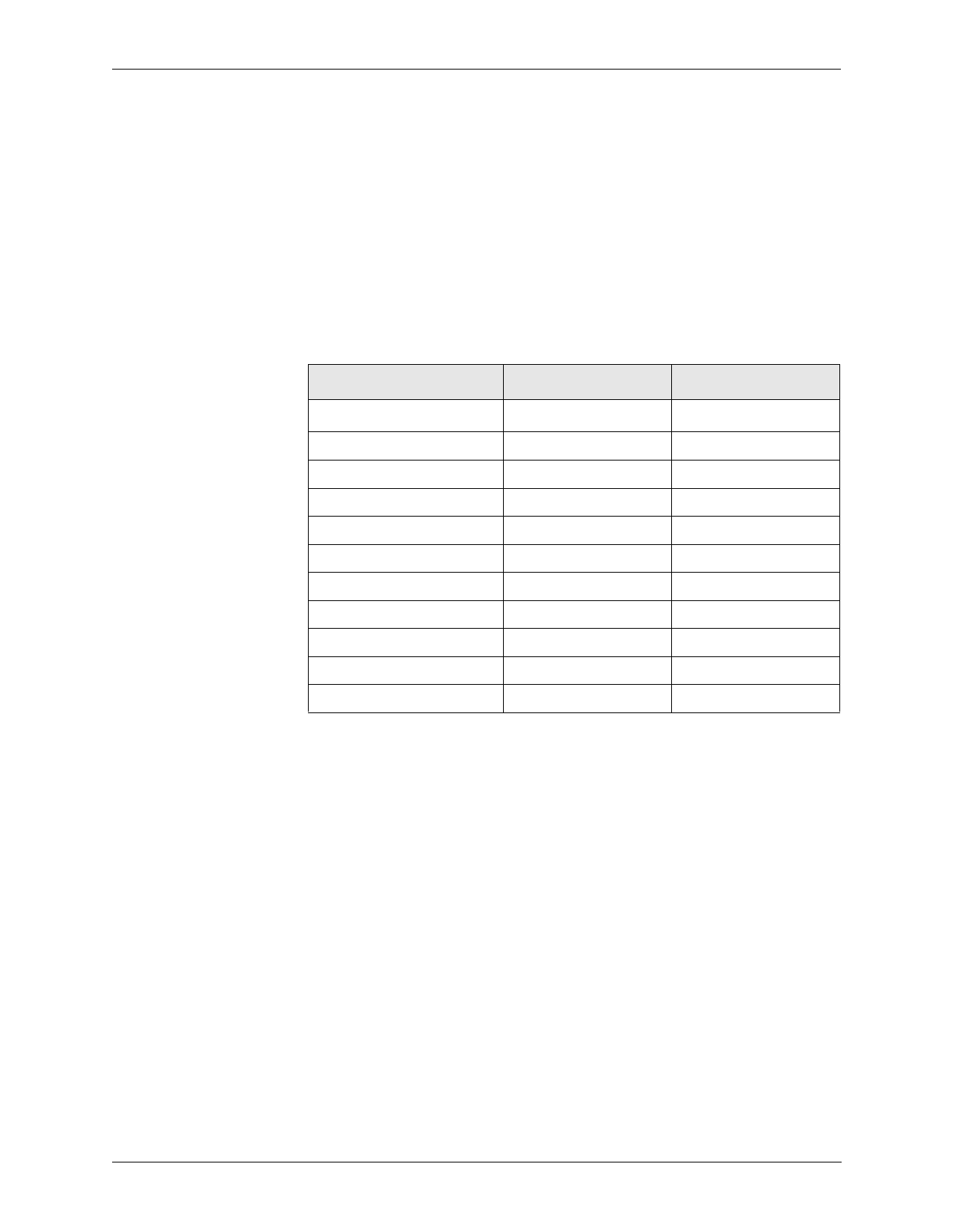

The connections for the Bt8110/8110B are given in Table C-1. Only 7 bits of

the address/data bus are required. Any one of the six upper address bits, A[13:8],

of the microprocessor can be used as a chip select signal. The Bt8110/8110B can

be operated by either a 8051-type or a 68HC11-type interface. Only the 8051-type

connections are given in Table C-1. For the 68HC11, the E signal must be

connected to WR* and the AS signal to ALE. The other connections are the same.

Table C-1. Bt8110/8110B Microprocessor Connection

ADPCM Processor Pin

Function

Intel 8051

MICREN

ALE

WR*

CS

AD[0]

AD[1]

AD[2]

AD[3]

AD[4]

AD[5]

AD[6]

Enable

Address Latch Enable

Write Enable

Chip Select

Address/Data

Address/Data

Address/Data

Address/Data

Address/Data

Address/Data

Address/Data

Vcc

ALE

WR*

A[n]

AD[0]

AD[1]

AD[2]

AD[3]

AD[4]

AD[5]

AD[6]

Table C-2 gives the address map and the bit interpretations of the control

fields. In this application address 0x40 must be set to a value of 0x1C to properly

set the mode of the Bt8110/8110B. A write to address 0x40 will cause the mode

of the Bt8110/8110B to be set. At least 750 ns must be allowed between

consecutive write operations to the Bt8110/8110B.

Table C-2 also provides the Per-Channel Control Register bit interpretations.

Bits D[3:0] of each encoder and decoder channel control select the particular

ADPCM code to be used; note that hex values of 6 and 7 are invalid for these bit

positions. ROM codes are available from Conexant. Bit D[6] enables A-law PCM

coding when set to 1. Bit D[5] enables the algorithm RESET function when set to

1. This operation sets the internal parameters of the Bt8110/8110B to fixed

values, as specified in ITU–T Recommendation G.726 and ANSI Standard

T1.303. Bit D[4] enables transparent operation when set to 1. For the encoder

channels, when the transparent bit is set, all 8 PCM bits are transferred to the

output with the same delay as when ADPCM decoding is taking place. For the

decoder, the five ADPCM inputs and two embedded-encoding inputs are

transferred to the PCM serial output with the same delay as when ADPCM

decoding is taking place. On the Bt8110 only, the input to PSIG[0], the least

significant bit, must be held at a logic low level in this application (this pin has an

internal pull-down resistor).

100060C

Conexant

C-5