ALC5633Q 데이터 시트보기 (PDF) - Realtek Semiconductor

부품명

상세내역

제조사

ALC5633Q Datasheet PDF : 87 Pages

| |||

ALC5633Q

Datasheet

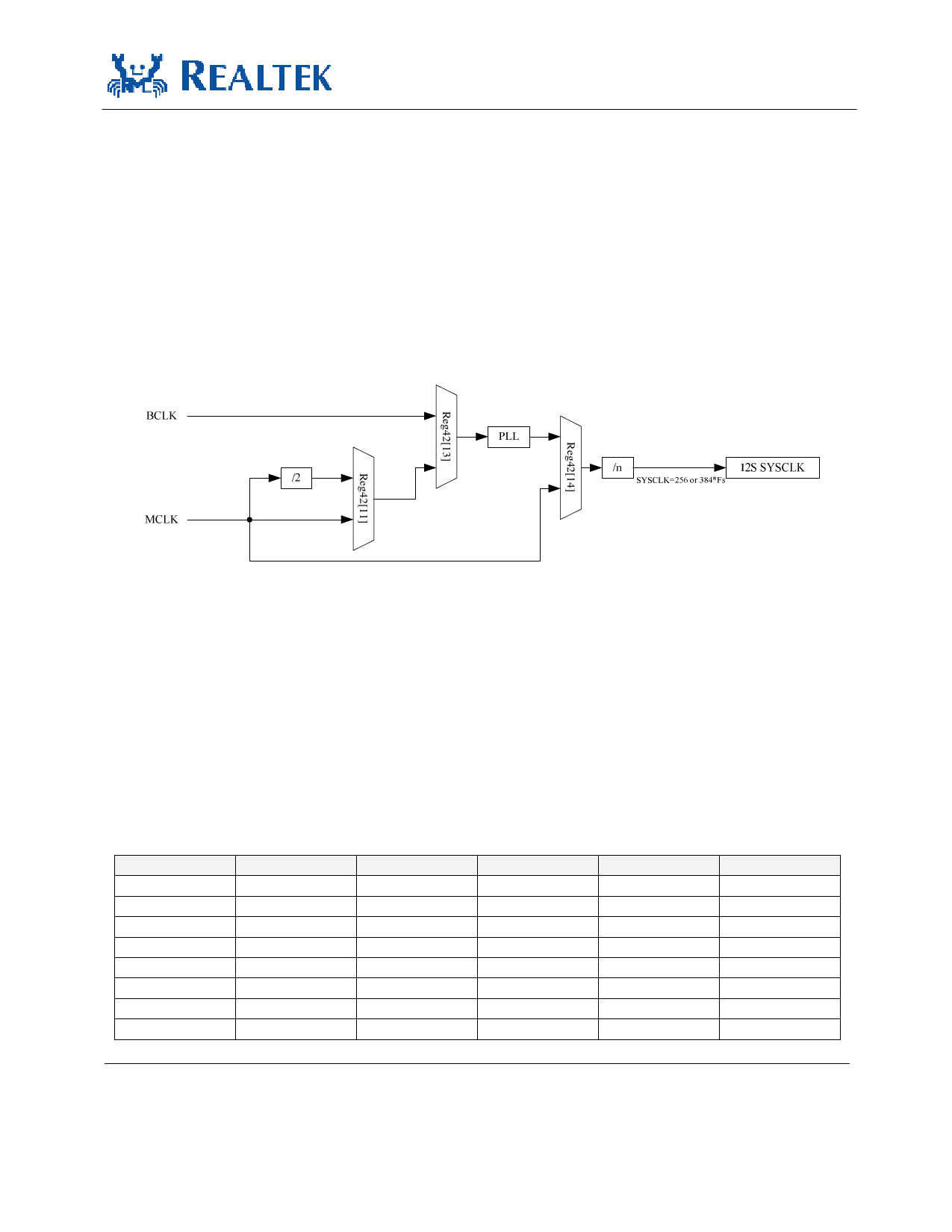

7.3. Clocking

The system clock of ALC5633Q can be selected from MCLK or PLL. MCLK is always provided

externally while the reference clock of PLLs can be selected from MCLK or BCLK.

The I2S_SYSCLK(Main SYSCLK) provides clocks into ADC that can be selected from MCLK or PLL.

The driver should arrange the clock of each block and setup each divider in order to provide

I2S_SYSCLK=256 or 384*Fs set by sel_adc_filter_clk as Audio internal system clock. Refer to Figure 3.

Audio SYSCLK

Figure 4. Audio Clock

7.3.1. Phase-Locked Loop

A Phase-Locked Loop (PLL) is used to provide a flexible input clock from 2.048MHz to 40MHz. The

source of the PLL can be set to MCLK or BCLK by setting register.

The driver can set up the PLL to output a frequency close to the system clock.

The PLL transmit formula is:

FOUT = (MCLK * (N+2)) / ((M+2) * (K+2)) {Typical K=2}

MCLK

13

3.6864

2.048

4.096

12

15.36

16

19.2

Table 7.

N

66

78

94

70

80

81

78

80

Clock Setting Table for 48K (Unit: MHz)

M

FVCO

K

7

98.222

2

1

98.304

2

0

98.304

2

1

98.304

2

8

98.4

2

11

98.068

2

11

98.462

2

14

98.4

2

FOUT

24.555

24.576

24.576

24.576

24.6

24.517

24.615

24.6

I2S Stereo Audio Codec + Mono Class-AB/D Amp

8

Rev. 0.1