UG80960HD5016SL2GM 데이터 시트보기 (PDF) - Intel

부품명

상세내역

제조사

UG80960HD5016SL2GM Datasheet PDF : 104 Pages

| |||

80960HA/HD/HT

3.1

Pin Descriptions

This section defines the 80960Hx pins. Table 6 presents the legend for interpreting the pin

descriptions in Table 7. All pins float while the processor is in the ONCE mode, except TDO,

which may be driven active according to normal JTAG specifications.

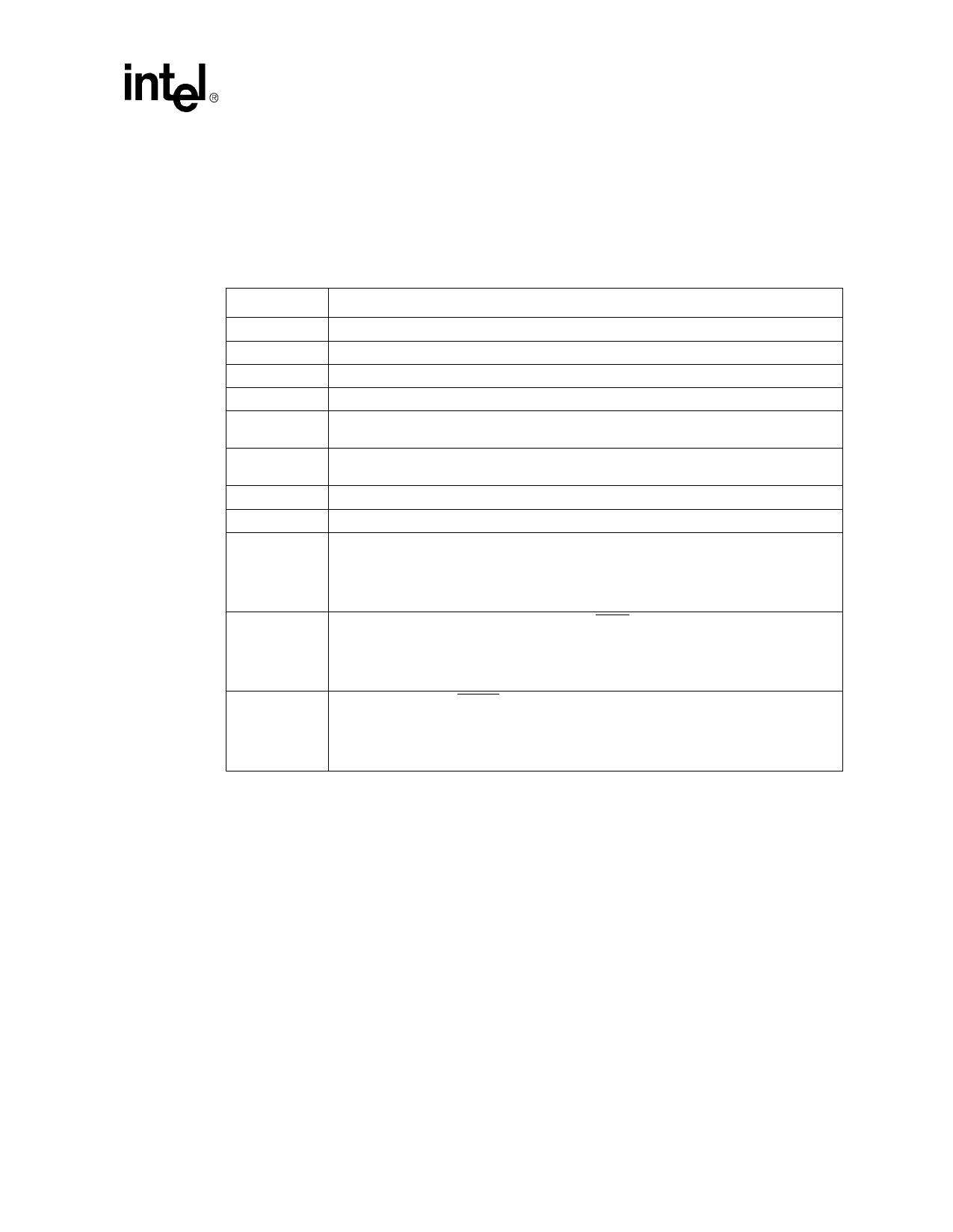

Table 6. Pin Description Nomenclature

Symbol

Description

I

O

I/O

-

S(E)

S(L)

A(E)

A(L)

H(...)

B(...)

R(...)

Input only pin.

Output only pin.

Pin may be input or output.

Pin must be connected as indicated for proper device functionality.

Synchronous edge sensitive input. This input must meet the setup and hold times relative to

CLKIN to ensure proper operation of the processor.

Synchronous level sensitive input. This input must meet the setup and hold times relative to

CLKIN to ensure proper operation of the processor.

Asynchronous edge-sensitive input.

Asynchronous level-sensitive input.

While the processor bus is in the HOLD state (HOLDA asserted), the pin:

H(1) is driven to VCC

H(0) is driven to VSS

H(Z) floats

H(Q) continues to be a valid output

While the processor is in the bus backoff state (BOFF asserted), the pin:

B(1) is driven to VCC

B(0) is driven to VSS

B(Z) floats

B(Q) continues to be a valid output

While the processor’s RESET pin is asserted, the pin:

R(1) is driven to VCC

R(0) is driven to VSS

R(Z) floats

R(Q) continues to be a valid output

Datasheet

15