DF8064101211300SR0VY 데이터 시트보기 (PDF) - Intel

부품명

상세내역

제조사

DF8064101211300SR0VY Datasheet PDF : 122 Pages

| |||

2.1

CPU Legacy Signal

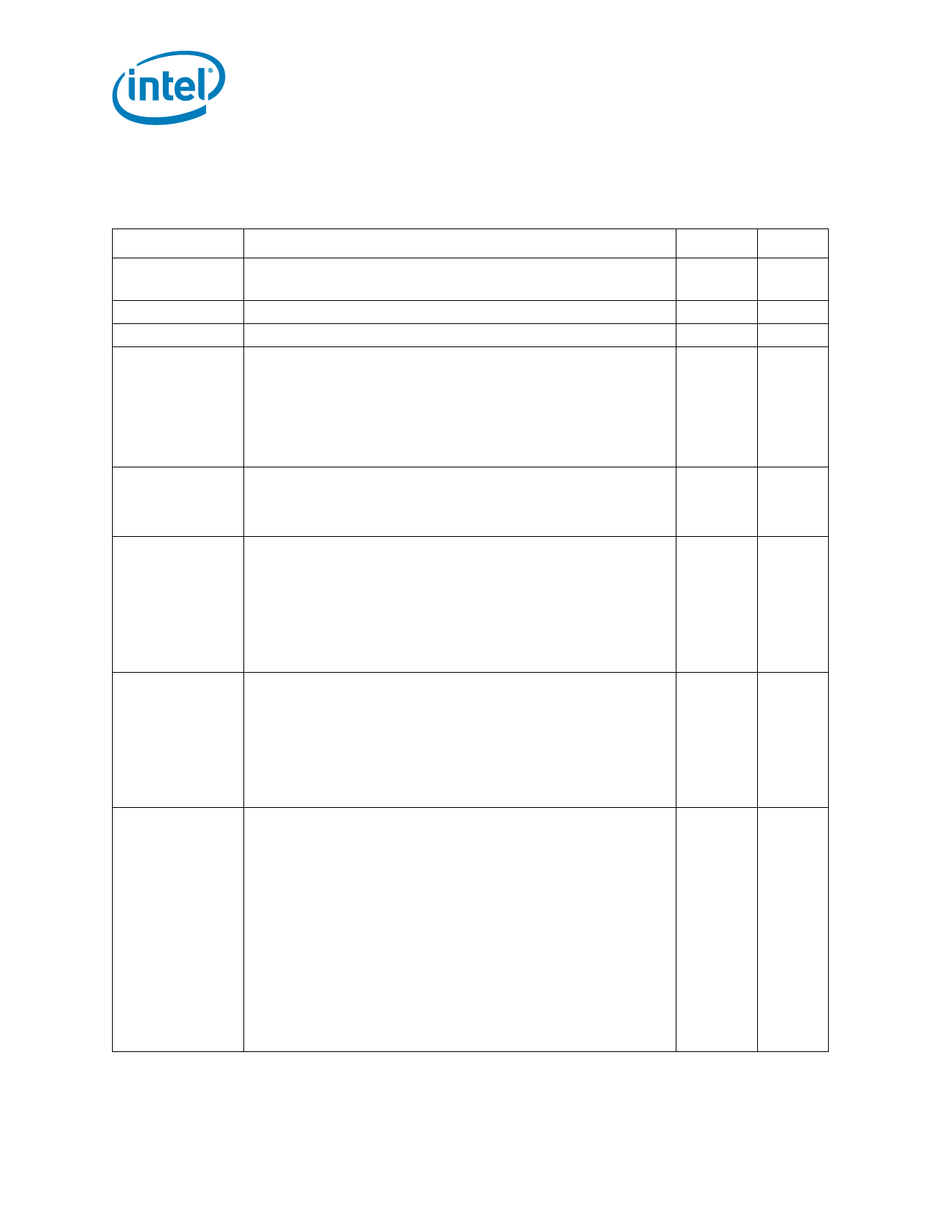

Table 2-6. CPU Legacy Signal (Sheet 1 of 2)

Signal Name

Description

Direction Type

EXTBGREF

External Band gap Reference. SOC and Core Debug feature.

HV_GPIO_RCOMP

MV_GPIO_RCOMP

PBE#

INIT#

INTR /LINT00

NMI/ LINT10

CPUPWRGOOD

RCOMP for 3.3V GPIO pins: 50 ohm 1% PD to VSS.

RCOMP for DFX_GPIO_GRPx pins: 50 ohm 1% PD to VSS.

When STPCLK# is not asserted, the Intel Atom Processor

D2000 series and N2000 series processor will always deassert

PBE#.

The Intel Atom Processor D2000 series and N2000 series

processor is always allowed to use PBE to request a break to C0 -

even if in C4 and in Deep Power Down Technology (code named

C6)

INIT# (Initialization), when asserted, resets integer registers

inside the processor without affecting its internal caches or

floating-point registers. CPU then restarts at the reset vector.

Snoops are handled during INIT# assertion.

Interrupt Request/Local APIC Interrupt 0: When the APIC is

disabled, the LINT0 signal becomes INTR, a maskable

asynchronous interrupt request signal.

This signal (and NMI/LINT1) must be software configured via BIOS

programming of the APIC register space to be used either as NMI/

INTR or LINT[1:0]. Because the APIC is enabled by default after

Reset, operation of these pins as LINT[1:0] is the default

configuration.

Non-Maskable Interrupt Request/Local APIC Interrupt 1: When the

APIC is disabled, the LINT1 signal becomes NMI, a non-maskable

asynchronous interrupt request signal.

This signal (and INTR/LINT0) must be software configured via

BIOS programming of the APIC register space to be used either as

NMI/INTR or LINT[1:0]. Because the APIC is enabled by default

after Reset, operation of these pins as LINT[1:0] is the default

configuration.

CPUPWRGOOD (Power Good) is a processor input. The processor

requires this signal to be a clean indication that the clocks and

power supplies are stable and within their specifications. ‘Clean’

implies that the signal will remain low (capable of sinking leakage

current), without glitches, from the time that the power supplies

are turned on until they come within specification. The signal must

then transition monotonically to a high state. Rise time and

monotonicity requirements are shown in Chapter 4 Electrical

Specifications. CPUPWRGOOD can be driven inactive at any time,

but clocks and power must again be stable before a subsequent

rising edge of CPUPWRGOOD. It must also meet the minimum

pulse width specification.

The CPUPWRGOOD signal must be supplied to the processor; it is

used to protect internal circuits against voltage sequencing issues.

It should be driven high throughout boundary scan operation.

I

Core

Analog

N/A

Analog

N/A

Analog

Core

O

Open

Drain

Core

I

CMOS

I

Core

CMOS

I

Core

CMOS

I

Core

CMOS

18

Datasheet - Volume 1 of 2