MC14LC5480P 데이터 시트보기 (PDF) - Motorola => Freescale

부품명

상세내역

제조사

MC14LC5480P Datasheet PDF : 24 Pages

| |||

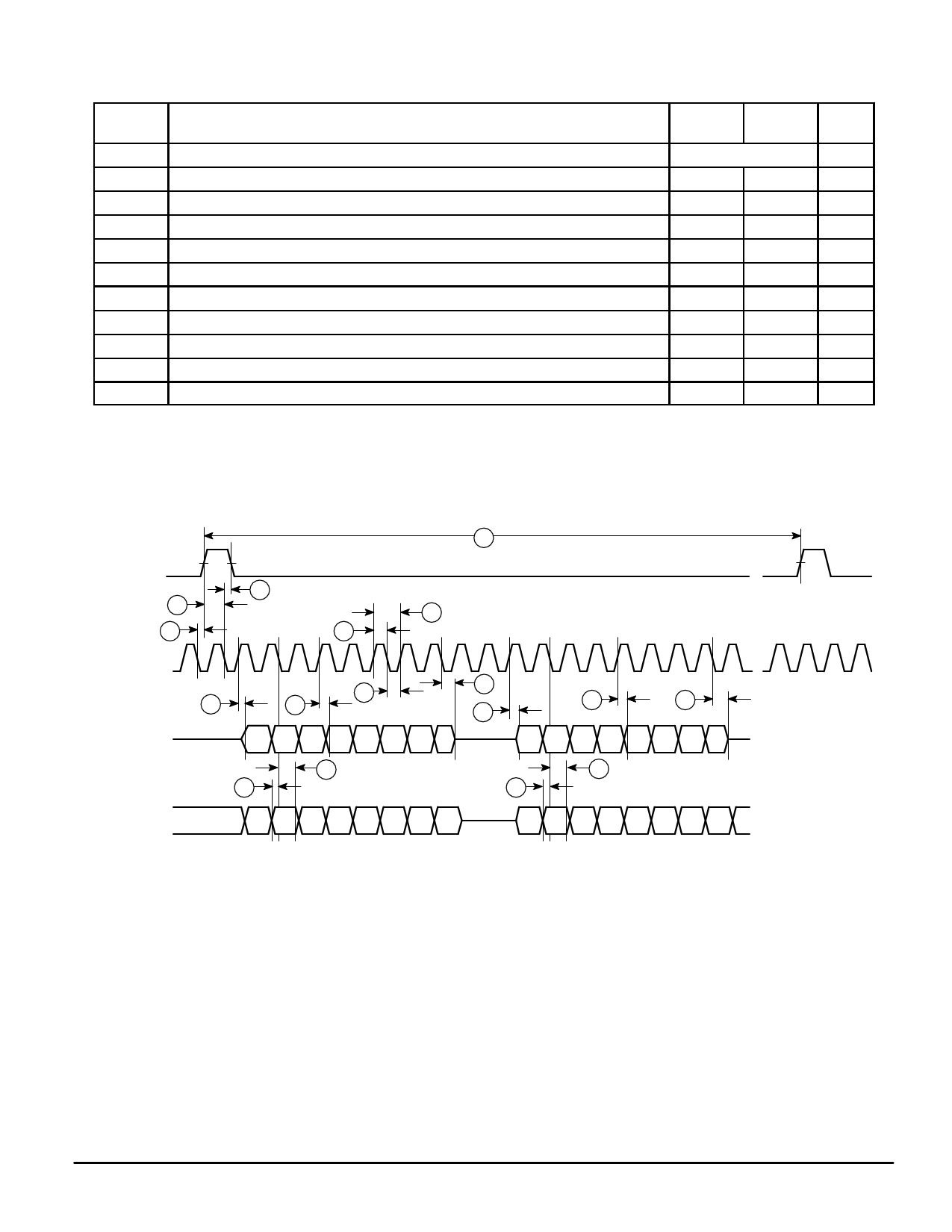

DIGITAL SWITCHING CHARACTERISTICS FOR IDL MODE

(VDD = 5.0 V ± 5%, TA = – 40 to + 85°C, CL = 150 pF, See Figure 5 and Note 1)

Ref.

No.

Characteristics

Min

Max

Unit

31

Time Between Successive IDL Syncs

Note 2

32

Hold Time of IDL SYNC After Falling Edge of IDL CLK

20

—

ns

33

Setup Time of IDL SYNC Before Falling Edge IDL CLK

60

—

ns

34

IDL Clock Frequency

256

4096

kHz

35

IDL Clock Pulse Width High

50

—

ns

36

IDL Clock Pulse Width Low

50

—

ns

37

Data Valid on IDL RX Before Falling Edge of IDL CLK

20

—

ns

38

Data Valid on IDL RX After Falling Edge of IDL CLK

75

—

ns

39

Falling Edge of IDL CLK to High–Z on IDL TX

10

50

ns

40

Rising Edge of IDL CLK to Low–Z and Data Valid on IDL TX

10

60

ns

41

Rising Edge of IDL CLK to Data Valid on IDL TX

—

50

ns

NOTES:

1. Measurements are made from the point at which the logic signal achieves the guaranteed minimum or maximum logic level.

2. In IDL mode, both transmit and receive 8–bit PCM words are accessed during the B1 channel, or both transmit and receive 8–bit PCM words

are accessed during the B2 channel as shown in Figure 5. IDL accesses must occur at a rate of 8 kHz (125 µs interval).

IDLE SYNC

(FST)

32

33

32

35

31

34

IDL CLOCK

(BCLKT)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

36

40

41

39

41

39

40

IDL TX

(DT)

MSB CH1 CH2 CH3 ST1 ST2 ST3 LSB

38

37

MSB CH1 CH2 CH3 ST1 ST2 ST3 LSB

38

37

IDL RX

(DR)

MSB CH1 CH2 CH3 ST1 ST2 ST3 LSB

MSB CH1 CH2 CH3 ST1 ST2 ST3 LSB

Figure 5. IDL Interface Timing

1

2

MC14LC5480

16

MOTOROLA