HD404394 데이터 시트보기 (PDF) - Hitachi -> Renesas Electronics

부품명

상세내역

제조사

HD404394 Datasheet PDF : 100 Pages

| |||

HD404344R Series/HD404394 Series

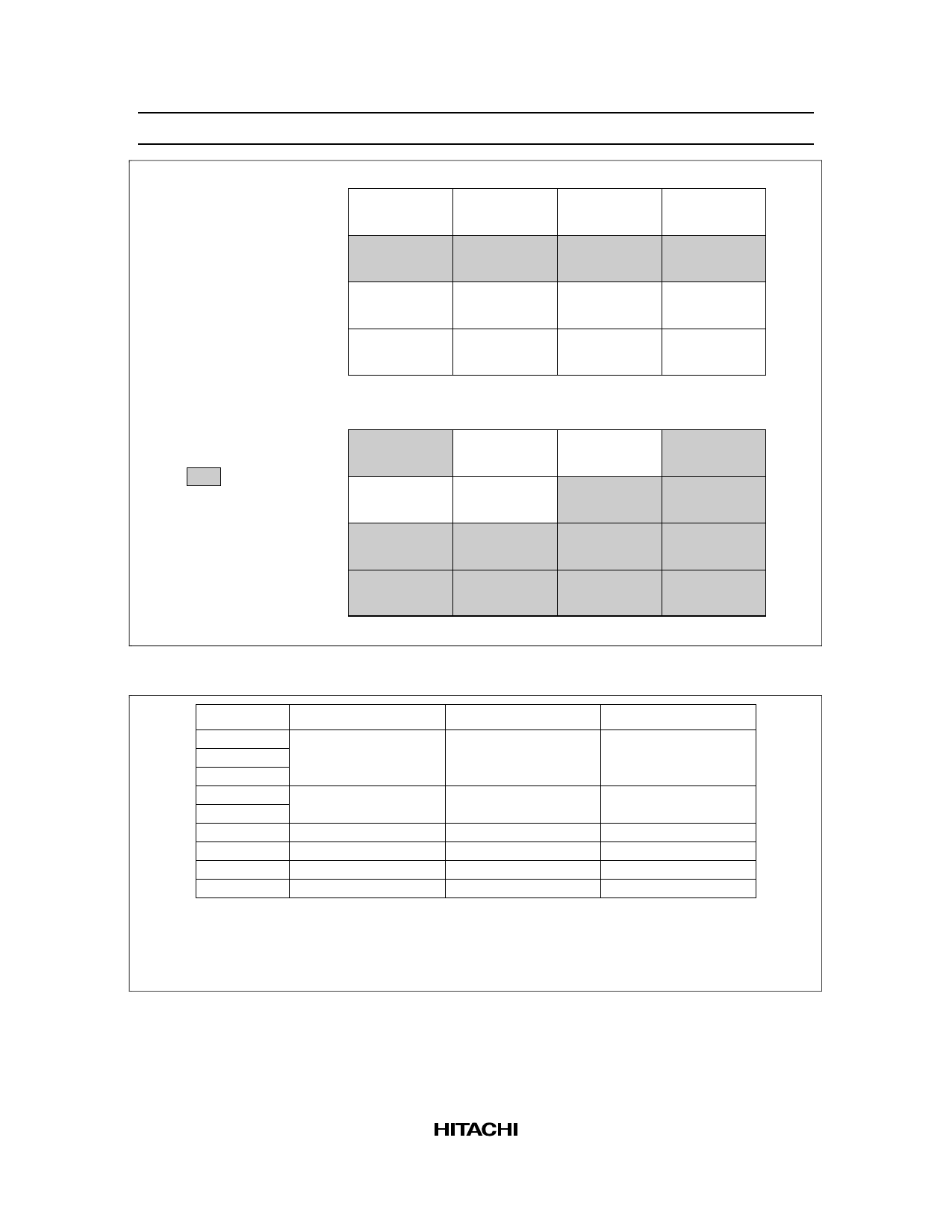

RAM Address

$0000

Bit 3

IM0

(IM of INT0)

$0001

Bit 2

IF0

(IF of INT0)

Bit 1

RSP

(Reset SP bit)

Bit 0

IE

(Interrupt

enable flag)

$0002

IMTC

(IM of timer C)

$0003

IMS

(IM of serial)

: Not used

IF: Interrupt

request flag

IE: Interrupt

mask

IM: Interrupt

enable flag

SP: Stack pointer

Bit 3

$020

$021

RAME

(RAM enable

flag)

$022

$023

IFTC

(IF of timer C)

IMTB

(IM of timer B)

IFS

(IF of serial)

IMAD

(IM of A/D)

Interrupt control bits area

Bit 2

ADSF

(A/D start flag)

IAOF

(IAD off flag)

Bit 1

WDON

(Watchdog

on flag)

Register flag area

IFTB

(IF of timer B)

IFAD

(IF of A/D)

Bit 0

Figure 3 Configuration of Interrupt Control Bits and Register Flag Areas

IE

IM

IAOF

IF

RAME

RSP

WDON

ADSF

Not used

SEM/SEMD

Can be used

Not processed

Not processed

Can be used

Can be used

Not processed

REM/REMD

Can be used

Can be used

Can be used

Not processed

Inhibited to access

Not processed

TM/TMD

Can be used

Can be used

Inhibited to access

Inhibited to access

Can be used

Inhibited to access

• The WDON bit can be reset by an MCU reset or by stop mode release with STOPC.

• Do not use REM/REMD for the ADSF bit during A/D conversion.

• If the TM or TMD instruction is excuted for the inhibited or non-existing bits, the value in

ST becomes invaild.

Figure 4 Limitations for RAM Bit Manipulation Instructions

18