EL5120 데이터 시트보기 (PDF) - Renesas Electronics

부품명

상세내역

제조사

EL5120 Datasheet PDF : 21 Pages

| |||

EL5120, EL5220, EL5420

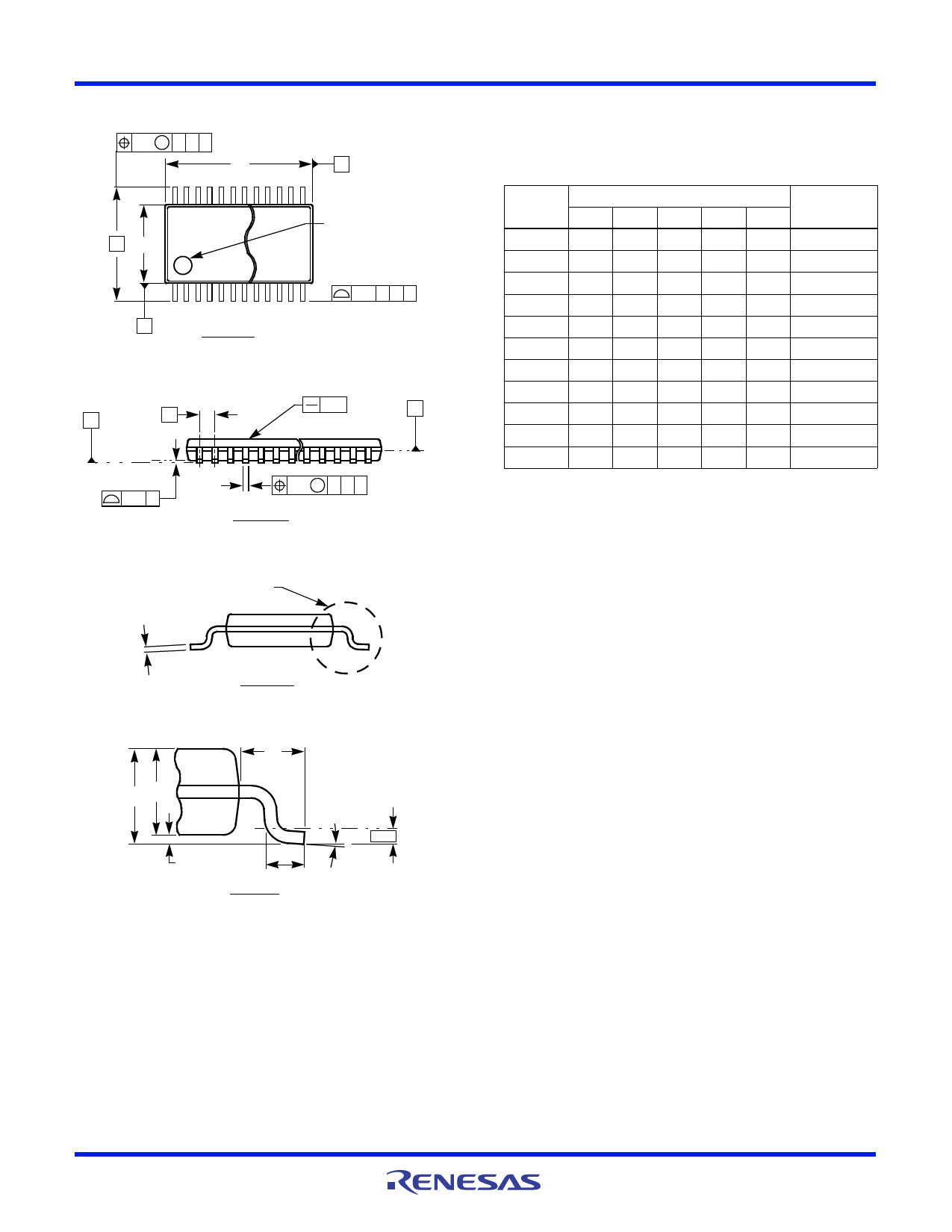

Thin Shrink Small Outline Package Family (TSSOP)

0.25 M C A B

D

A

N

(N/2)+1

E E1

PIN #1 I.D.

1

B

TOP VIEW

(N/2)

0.20 C B A

2X

N/2 LEAD TIPS

C

e

0.05

H

SEATING

PLANE

0.10 C

N LEADS

b

0.10 M C A B

SIDE VIEW

SEE DETAIL ‚Äö

MDP0044

THIN SHRINK SMALL OUTLINE PACKAGE FAMILY

MILLIMETERS

SYMBOL 14 LD 16 LD 20 LD 24 LD 28 LD TOLERANCE

A

1.20 1.20 1.20 1.20 1.20

Max

A1

0.10 0.10 0.10 0.10 0.10

±0.05

A2

0.90 0.90 0.90 0.90 0.90

±0.05

b

0.25 0.25 0.25 0.25 0.25 +0.05/-0.06

c

0.15 0.15 0.15 0.15 0.15 +0.05/-0.06

D

5.00 5.00 6.50 7.80 9.70

±0.10

E

6.40 6.40 6.40 6.40 6.40

Basic

E1

4.40 4.40 4.40 4.40 4.40

±0.10

e

0.65 0.65 0.65 0.65 0.65

Basic

L

0.60 0.60 0.60 0.60 0.60

±0.15

L1

1.00 1.00 1.00 1.00 1.00 Reference

NOTES:

Rev. F 2/07

1. Dimension “D” does not include mold flash, protrusions or gate

burrs. Mold flash, protrusions or gate burrs shall not exceed

0.15mm per side.

2. Dimension “E1” does not include interlead flash or protrusions.

Interlead flash and protrusions shall not exceed 0.25mm per

side.

3. Dimensions “D” and “E1” are measured at dAtum Plane H.

4. Dimensioning and tolerancing per ASME Y14.5M-1994.

c

END VIEW

A A2

A1

L1

L

DETAIL X

GAUGE

PLANE

0.25

0¬¨¬®Ðê

FN7186 Rev 8.00

October 15, 2015

Page 18 of 21