MSM62X42B 데이터 시트보기 (PDF) - Oki Electric Industry

부품명

상세내역

제조사

MSM62X42B Datasheet PDF : 27 Pages

| |||

¡ Semiconductor

MSM62X42B

MASK BIT

"0"

STD.P

OUTPUT

IN TRT/STND BIT = "0"

"1"

"1" OUTPUT DOES NOT OCCUR

AT LOW LEVEL BECAUSE

"0"

MASK BIT IS "1"

OPEN

LOW LEVEL

OUTPUT TIMING

AUTOMATIC RETURN

(When “0” is written to IRQ FLAG bit, at that time, STD.P

output becomes open without awaiting automatic return.)

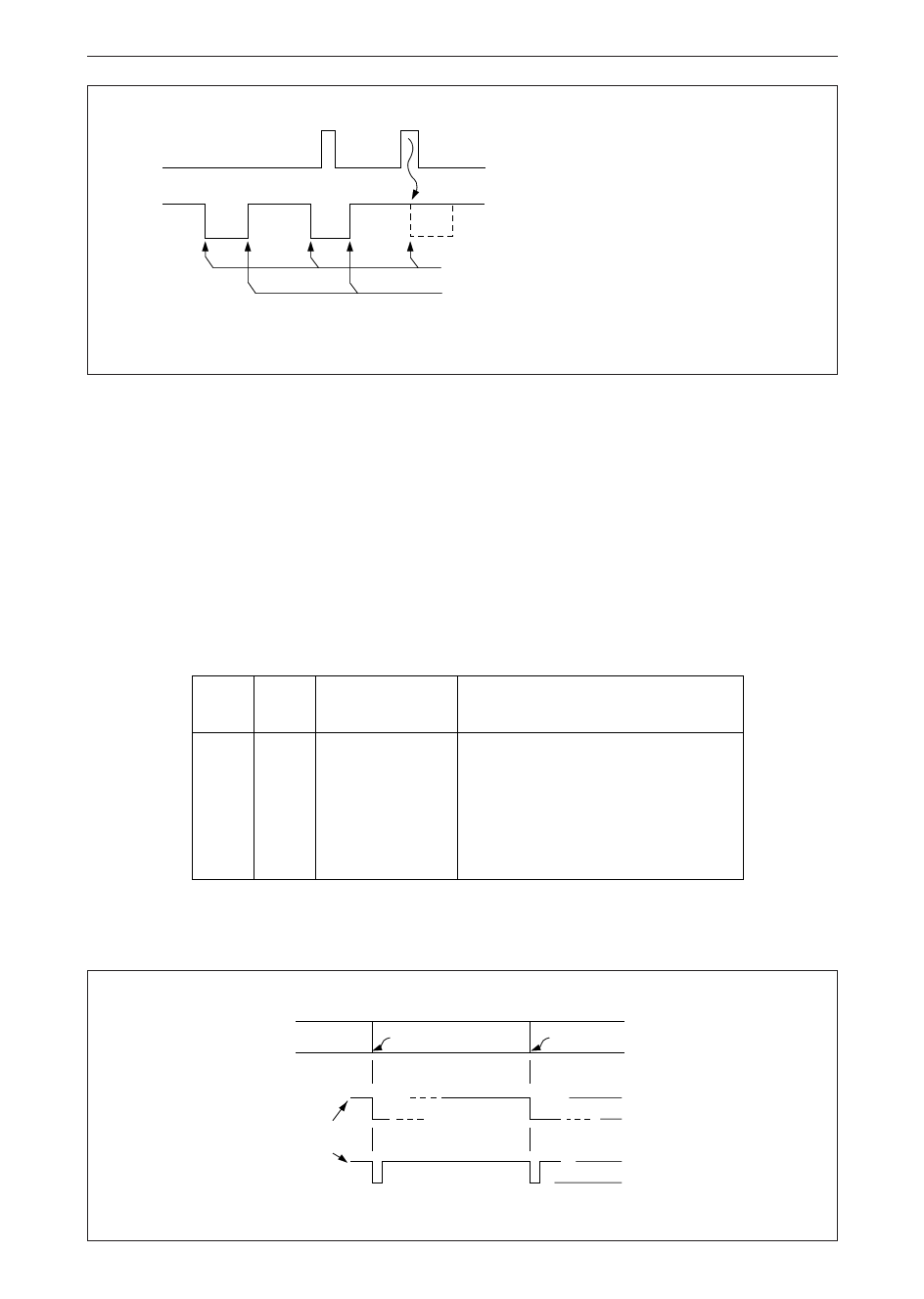

b) ITRPT/STND (D1) (INTERRUPT/STANDARD PULSE)

This is a bit which gives the meaning for STD.P output. When this bit="1", the request for

interrupt is outputted at the STD.P output and when this bit="0", a fixed cycle waveform with

a low-level pulse width of 7.8125ms is present at the STD.P output. However, at this time,

the MASK bit must equal 0, while the period in either modes is determined by t0 (D2) and

t1(D3) of register CE.

c) t0 (D2), t1 (D2) (time 0, 1)

• When ITRPT/STND bit="1", this bit determines the interrupt period. When ITRPT/

STND bit="0", this bit determines the period of fixed timing waveform. The periods are

shown in the table below.

t1

t0

0

0

0

1

1

0

1

1

Period

1/64 second

1 second

1 minute

1 hour

Duty CYCLE of "L" level when

INRPT/STND bit is "0".

1/2

1/128

1/7680

1/460800

• The timing of the STD.P output designated by t1 and t2 occurs at the moment that a carry

occurs to a clock digit.

(EXAMPLE) WHEN t1 = 1, t0 = 1 and MASK = 0

PM12:00

PM1:00

WHEN ITRPT/STND

BIT is "1"

STD.P OUTPUT

WHEN ITRPT/STND

BIT is "0"

OPEN

LOW LEVEL

OPEN

LOW LEVEL

The special counter is not included for t1 and t0.

55