LC74201JE 데이터 시트보기 (PDF) - SANYO -> Panasonic

부품명

상세내역

제조사

LC74201JE Datasheet PDF : 21 Pages

| |||

LC74201JE

Block Descriptions

1. CD-ROM decoder

This block takes the MPEG bit stream from the external CD digital signal processor and decodes it in accordance

with the CD-ROM standard.

• The decoded data is automatically transferred to the next stage, the system decoder.

• Storing the decoded data in DRAM is also possible.

• The high-speed decoder core supports quadruple-speed playback.

• Internal registers offer settings for connecting to most commercially available CD digital signal processors.

— 32- or 24-slot

— LSB or MSB first

— Front- or rear-justification for data

— Rising or falling edge for bit clock

• The video CD’s track 1 data can be stored in a user area set aside in the external DRAM. The user area capacity

can be selected from 4 K to 22 Kbytes according to the external DRAM capacity.

• An auto restart function stores the address of the last sector accessed before a pause so that playback can resume at

the next sector when the pause ends.

• The contents of the sector header and subheader are available from registers.

2. System decoder

This block analyzes the MPEG bit stream, splits it into video and audio bit streams, and transfers these bit streams to

the corresponding decoders. It calculates the decode start timing from the time stamp and the decoders’ inherent

delays and generates the necessary start signals to provide automatic synchronization of audio and video outputs.

3. CPU interface

This interface allows the CPU to access the internal registers to set parameters controlling operation and to read out

operational status. It may be configured as either an 8-bit parallel interface multiplexing data and addresses or as a

4-wire serial interface.

4. Audio decoder

This block decodes the MPEG1 audio bit stream from the system decoder in accordance with the ISO11172-3

standard.

• The use of 24-bit internal precision yields high audio quality.

• The decoder supports all MPEG audio modes defined for layers 1 and 2 except the free format mode.

• Internal registers offer settings for connecting to most commercially available D/A converters.

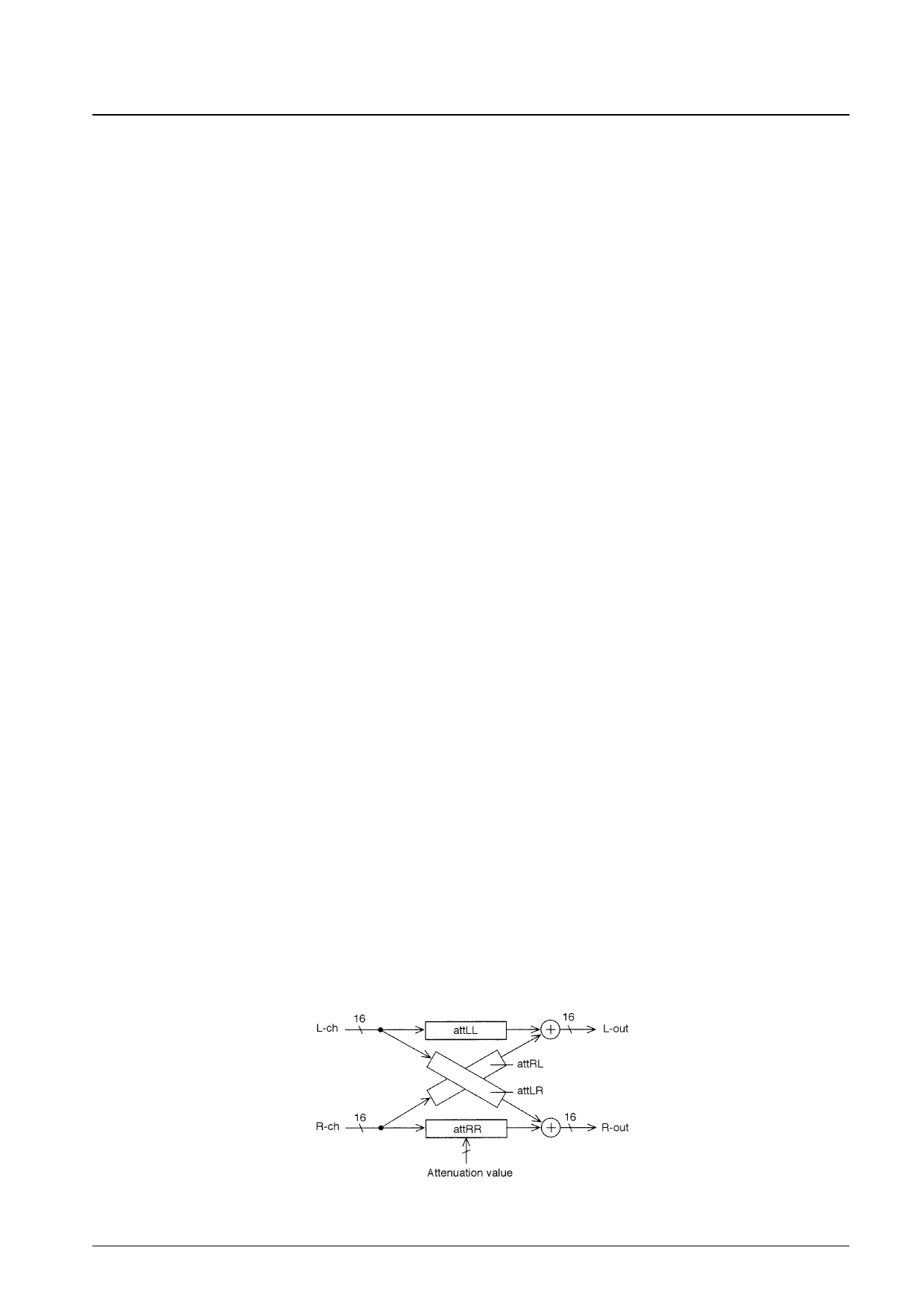

• The block includes a cross attenuator compliant with the CD-i standard.

• The block supports readout of the frame header data.

• The block performs CRC checking. If there is an error, it automatically substitutes the preceding frame stored in

DRAM. If there are continuous errors, it switches to muting.

• The output format of audio D/A converter’s interface may be selected between normal output and open-drain

output in accordance with the D/A converter input level.

8

Cross Attenuator

No. 5761-8/21