USS-820D 데이터 시트보기 (PDF) - Agere -> LSI Corporation

부품명

상세내역

제조사

USS-820D Datasheet PDF : 58 Pages

| |||

Data Sheet, Rev. 4

June 2001

USS-820D

USB Device Controller

Description (continued)

FIFO Access (continued)

Transmit FIFO

The transmit FIFOs are circulating data buffers that have the following features:

I Support up to two separate data sets of variable sizes (dual-packet mode).

I Include byte counter register for storing the number of bytes in the data sets.

I Protect against overwriting data in a full FIFO.

I Can retransmit the current data set.

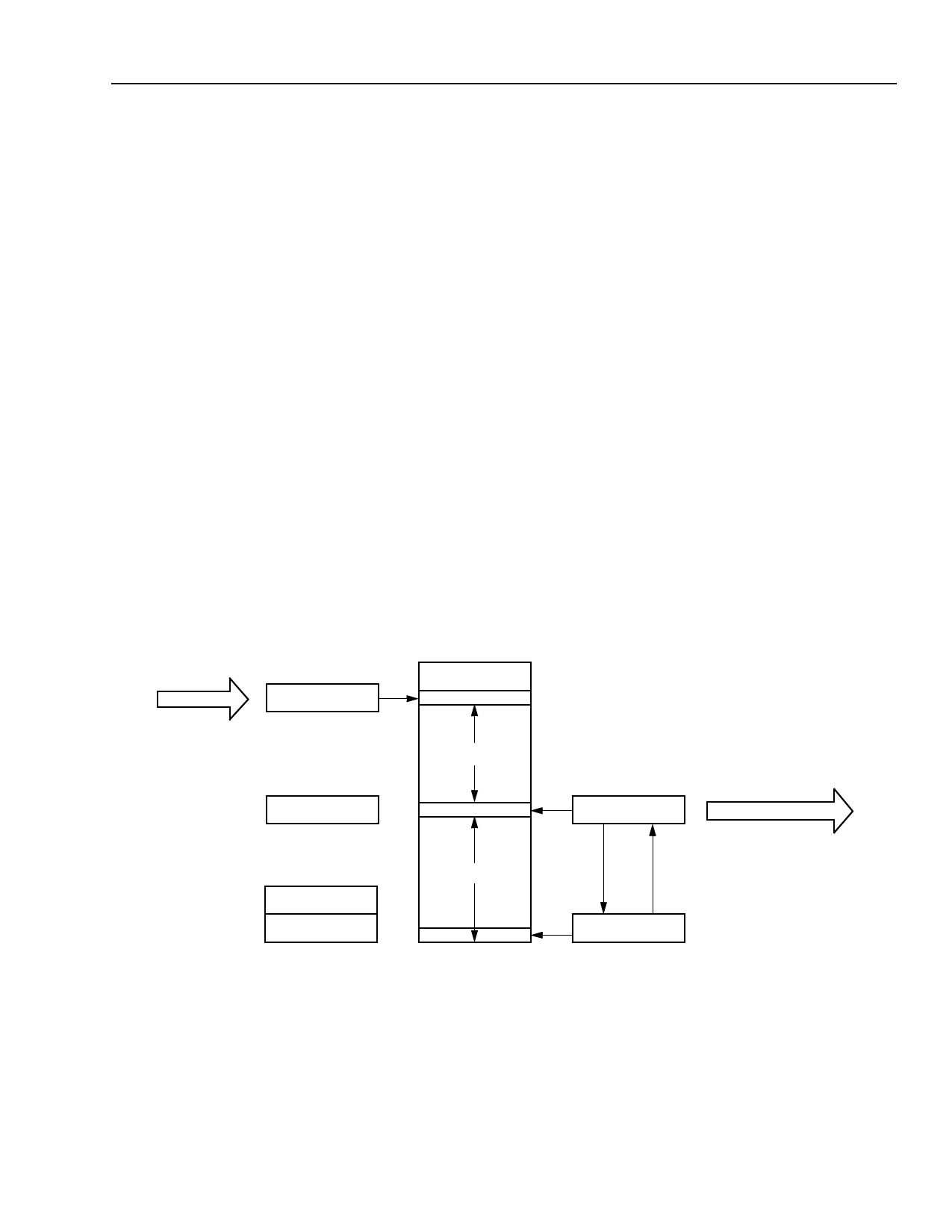

All transmit FIFOs use the same architecture (see Figure 2). The transmit FIFO and its associated logic can man-

age up to two data sets: data set 0 (ds0) and data set 1 (ds1). Since two data sets can be used in the FIFO, back-

to-back transmissions are supported. Dual-packet mode for transmit FIFOs is enabled by default. Single-packet

mode can be enforced by firmware convention (see TXFIF register bits).

The CPU writes to the FIFO location that is specified by the write pointer. After a write, the write pointer automati-

cally increments by 1. The read marker points to the first byte of data written to a data set, and the read pointer

points to the next FIFO location to be read by the USB interface. After a read, the read pointer automatically incre-

ments by 1.

When a good transmission is completed, the read marker can be advanced to the position of the read pointer to set

up for reading the next data set. When a bad transmission is completed, the read pointer can be reversed to the

position of the read marker to enable the function interface to reread the last data set for retransmission. The read

marker advance and read pointer reversal can be achieved two ways: explicitly by firmware or automatically by

hardware, as indicated by bits in the transmit FIFO control register (TXCON).

FROM CPU

WRITE POINTER

CPU

WRITES TO FIFO

TXDAT

BYTE COUNT

REGISTERS

TXCNTH

TXCNTL

DATA SET 1

SIE READS FIFO

READ POINTER

TO USB INTERFACE

DATA SET 0

REVRP

ADVRM

READ MARKER

Figure 2. Transmit FIFO

5-5206

Agere Systems Inc.

5