ADCMP606(Rev0) 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

제조사

ADCMP606

(Rev.:Rev0)

(Rev.:Rev0)

ADCMP606 Datasheet PDF : 16 Pages

| |||

ADCMP606/ADCMP607

APPLICATION INFORMATION

POWER/GROUND LAYOUT AND BYPASSING

The ADCMP606/ADCMP607 comparators are very high speed

devices. Despite the low noise output stage, it is essential to use

proper high speed design techniques to achieve the specified

performance. Because comparators are uncompensated

amplifiers, feedback in any phase relationship is likely to cause

oscillations or undesired hysteresis. Of critical importance is the

use of low impedance supply planes, particularly the output

supply plane (VCCO) and the ground plane (GND). Individual

supply planes are recommended as part of a multilayer board.

Providing the lowest inductance return path for switching

currents ensures the best possible performance in the target

application.

It is also important to adequately bypass the input and output

supplies. Multiple high quality 0.01 μF bypass capacitors should

be placed as close as possible to each of the VCCI and VCCO supply

pins and should be connected to the GND plane with redundant

vias. At least one of these should be placed to provide a physically

short return path for output currents flowing back from ground

to the VCC pin. High frequency bypass capacitors should be

carefully selected for minimum inductance and ESR. Parasitic

layout inductance should also be strictly controlled to maximize

the effectiveness of the bypass at high frequencies.

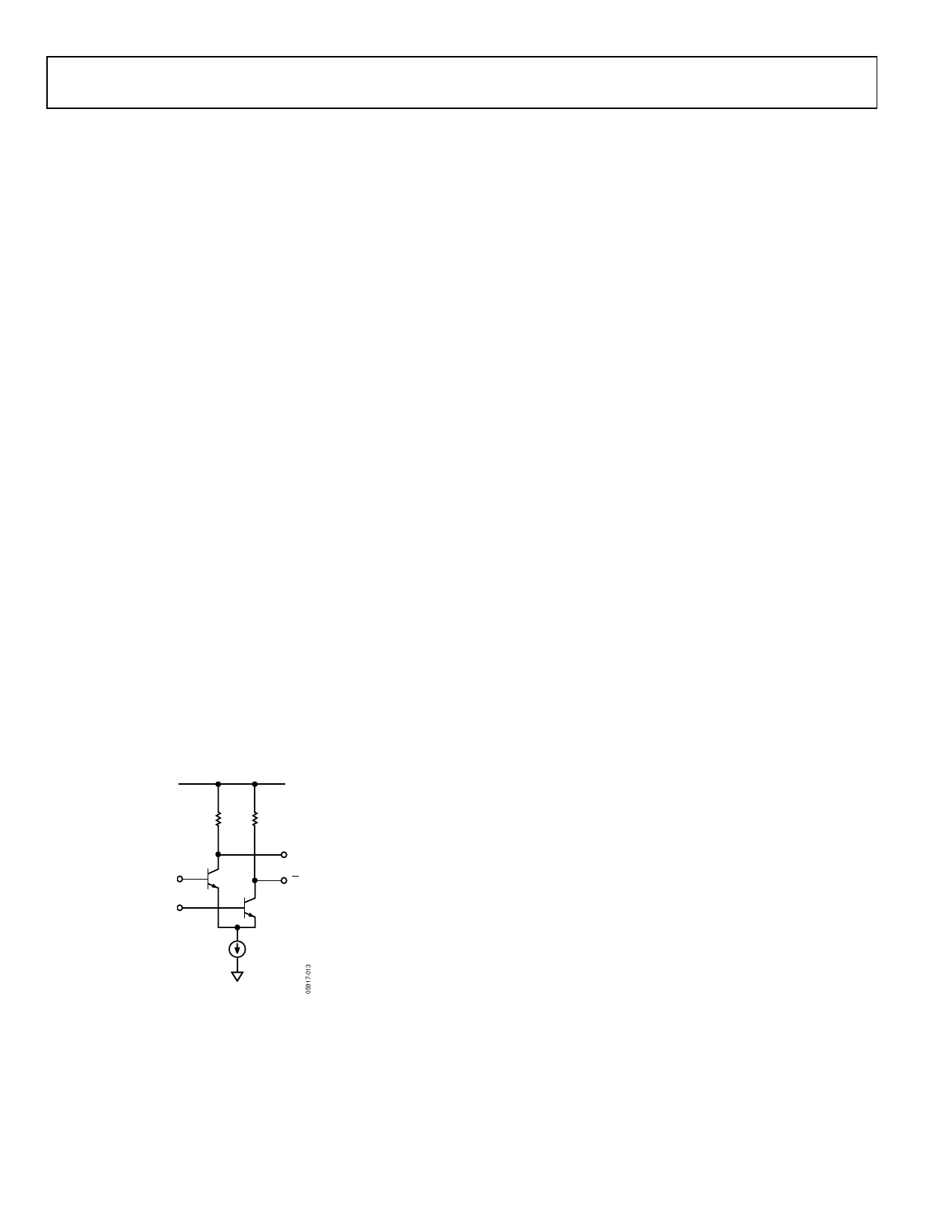

CML-COMPATIBLE OUTPUT STAGE

Specified propagation delay dispersion performance can be

achieved by using proper transmission line terminations. The

outputs of the ADCMP606 and ADCMP607 are designed to drive

400 mV directly into a 50 Ω cable or into transmission lines

terminated using either microstrip or strip line techniques with

50 Ω referenced to VCC. The CML output stage is shown in the

simplified schematic diagram in Figure 14. Each output is back-

terminated with 50 Ω for best transmission line matching.

VCCO

50Ω

Q

Q

16mA

GND

Figure 14. Simplified Schematic Diagram of

CML-Compatible Output Stage

If these high speed signals must be routed more than a

centimeter, then either microstrip or strip line techniques are

required to ensure proper transition times and to prevent

excessive output ringing and pulse width dependent

propagation delay dispersion.

It is also possible to operate the outputs with the internal

termination only if greater output swing is desired. This can be

especially useful for driving inputs on CMOS devices intended

for full swing ECL and PECL, or for generating pseudo PECL

levels. To avoid deep saturation of the outputs and resulting

pulse dispersion, VCCO must be kept above the specified

minimum output low level (see the Electrical Characteristics

section). The line length driven should be kept as short as

possible.

USING/DISABLING THE LATCH FEATURE

The latch input is designed for maximum versatility. It can

safely be left floating or it can be driven low by any standard

TTL/CMOS device as a high speed latch.

In addition, the pin can be operated as a hysteresis control pin

with a bias voltage of 1.25 V nominal and an input resistance of

approximately 7000 Ω. This allows the comparator hysteresis to

be easily controlled by either a resistor or an inexpensive CMOS

DAC. Driving this pin high or floating the pin removes all

hysteresis.

Hysteresis control and latch mode can be used together if an

open drain, an open collector, or a three-state driver is connected

parallel to the hysteresis control resistor or current source.

Due to the programmable hysteresis feature, the logic threshold

of the latch pin is approximately 1.1 V regardless of VCC.

OPTIMIZING PERFORMANCE

As with any high speed comparator, proper design and layout

techniques are essential for obtaining the specified performance.

Stray capacitance, inductance, inductive power and ground

impedances, or other layout issues can severely limit performance

and often cause oscillation. Large discontinuities along input

and output transmission lines can also limit the specified pulse

width dispersion performance. The source impedance should

be minimized as much as is practicable. High source impedance,

in combination with the parasitic input capacitance of the

comparator, causes an undesirable degradation in bandwidth at

the input, thus degrading the overall response. Thermal noise

from large resistances can easily cause extra jitter with slowly

slewing input signals; higher impedances encourage undesired

coupling.

Rev. 0 | Page 10 of 16