ADP3203 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

제조사

ADP3203 Datasheet PDF : 16 Pages

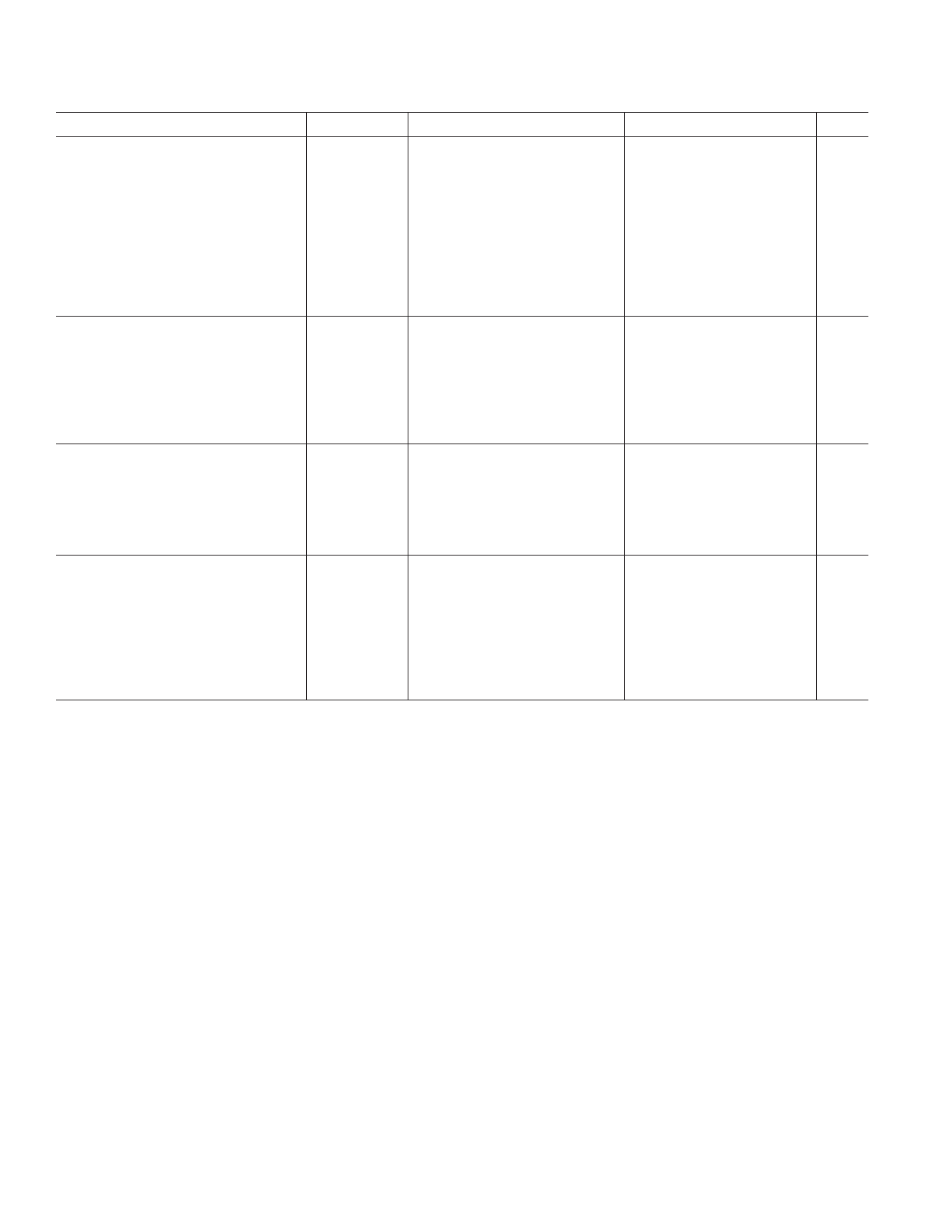

| |||

ADP3203

Parameter

SHIFT SETTING

Battery Shift Current

Battery Shift Reference Voltage

Deep Sleep Shift Current

Deep Sleep Shift Reference Voltage

SHIFT CONTROL INPUTS

BOM Threshold

(CMOS Input)

DSLP Threshold

(VTT-Level CMOS Input)

DPRSLP Mode Threshold8

(CMOS Input)

LOW SIDE DRIVE CONTROL

Output Voltage (CMOS Output)

Output Current

Symbol

Conditions

IRAMPB, ICS+B

VBSHIFT

VVID = 1.25 V

IBSHIFT = –100 µA, BOM = L

DSLP = H

IRAMPD, ICS+D

VDSHIFT

VVID = 1.25 V

IDSHIFT = –100 µA, BOM = H

DSLP = L

VBOM

VDSLP

VDPRSLP

Min Typ

–92.5 –100

–92.5

VDAC

–100

VDAC

VCC/2

0.9

VCC/2

VDRVLSD

IDRVLSD

DPRSLP = H

DPRSLP = L

DPRSLP = H, VDRVLSD = 1.5 V

DPRSLP = L, VDRVLSD = 1.5 V

0

0.7 VCC

0.4

–0.4

Max Unit

–107.5 mA

V

–107.5 mA

V

V

V

V

0.4

V

VCC

V

mA

mA

OVER/REVERSE VOLTAGE

PROTECTION-CORE FEEDBACK

Overvoltage Threshold

Reverse Voltage Threshold

Output Voltage

VCOREFB,OVP

VCOREFB,OVP

VCOREFB Rising

VCOREFB Falling

2.0

V

–0.3

V

(Open-Drain Output)

Output Current

VCLAMP

ICLAMP

VCOREFB = 2.2 V, VCLAMP = 5 V

VCOREFB = VDAC, VCLAMP = 5 V

0.7 VCC

2

4

VCC

V

10

µA

mA

NOTES

1All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods.

2Guaranteed by characterization.

3Two test conditions: 1)PWRGD is OK but forced to fail by applying an out-of-the-Core-Good-window voltage (V COREFB,BAD = 1.0 V at VVID = 1.25 V setting) to the

COREFB pin right after the moment that BOM or DPRSLP is asserted/deasserted. PWRGD should not fail immediately, only with the specified blanking delay

time. 2) PWRGD is forced to fail (VCOREFB, BAD = 1.0 V at VVID = 1.25 V setting) but gets into the Core Good window

(VCOREFB, GOOD = 1.25 V) right after the moment that BOM or DPRSLP is asserted/deasserted. PWRGD should not go high immediately, only with the specified

blanking delay time.

4Guaranteed by design.

5 Measured from 50% of VID code transition amplitude to the point where VDACOUT settles within ± 1% of its steady state value.

640 mVp-p amplitude impulse with 20 mV overdrive. Measured from the input threshold intercept point to 50% of the output voltage swing.

7Measured between the 30% and 70% points of the output voltage swing.

8DPRSLP circuit meets the minimum 30 ns DPRSLPVR signal assertion requirement; guaranteed by design.

–4–

REV. 0