ATC35 데이터 시트보기 (PDF) - Atmel Corporation

부품명

상세내역

제조사

ATC35 Datasheet PDF : 14 Pages

| |||

ATC35 Summary

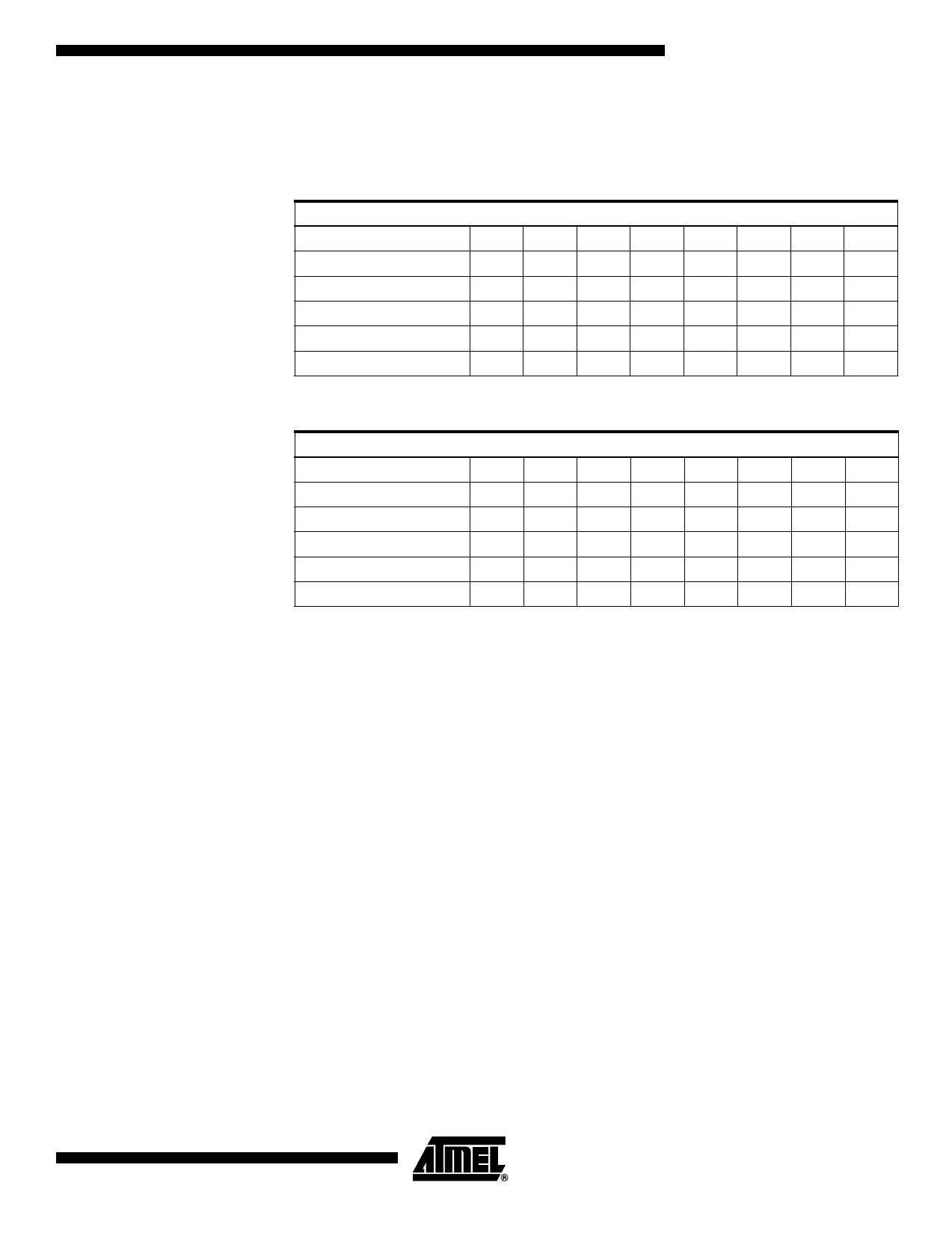

The following tables show the range of performances for particular ARAM configura-

tions without BIST and without CLoad. Access time (tACC) and cycle time (tCYC) refer to

Max industrial conditions, whereas Dynamic Power dissipation refers to typical

conditions.

Word Depth

Width (mm)

Height (mm)

Access Time (tACC) (nsec)

Cycle Time (tCYC) (nsec)

Dynamic Power (mW/MHz)

256

0.264

0.609

5.53

5.53

0.20

Word Size = 8

512

1K

2K

0.430 0.430 1.514

0.634 1.078 0.647

5.78 6.52 7.08

5.78 6.74 7.08

0.33 0.43 0.29

4K

1.514

1.091

7.81

8.26

0.37

8K

2.844

1.097

8.62

9.10

0.64

16K

5.607

1.097

9.36

9.74

0.84

32K

5.607

1.984

10.83

12.68

0.96

Word Depth

Width (mm)

Height (mm)

Access Time (tACC) (nsec)

Cycle Time (tCYC) (nsec)

Dynamic Power (mW/MHz)

128

0.430

0.387

5.33

5.33

0.26

Word Size = 16

256

512

1K

0.430 0.765 0.765

0.609 0.634 1.078

5.70 5.95 6.69

5.70 5.95 6.94

0.39 0.66 0.85

2K

2.852

0.647

8.38

8.38

0.63

4K

2.852

1.091

9.11

9.54

0.79

8K

5.607

1.091

9.86

10.18

1.08

16K

5.607

1.978

11.33

13.12

1.22

Compiled Dual-Port RAM

Megacells

The Atmel Dual-Port RAM is a read/write memory that allows access to and from its

memory cells by two independent ports (identified as Port A and Port B). There are no

constraints on the timing of the ports relative to each other except in the case of address

contention. Although the ports are constructed from the same circuitry, the possible I/O

configurations are different:

• Port A may be selected with read/write or read-only capability

• Port B can have read/write or write-only capability

The two ports may have different wordlengths, provided that the ratio is an integral

power of 2 (1, 2, 4, 8, 16, 32 or 64). The product (wordlength x address space) must be

the same for the two ports.

The memory cell corresponds to a standard full CMOS six-transistor cell with the benefit

of extremely low standby power dissipation. (There are actually eight or ten transistors

per cell, according to the configuration of the port A).

Dual-Port RAM operates in single-edge clock controlled mode during read operations,

and a double-edge controlled mode during write operations. Addresses are clocked

internally on the rising edge of the clock signal (ME). Any change of address without ris-

ing edge of ME is not considered.

In read mode, the rising clock edge triggers a data read without any significant con-

straint on the length of the ME pulse. In write mode, data applied to the inputs is latched

on the falling edge of ME or the rising edge of WE_, whichever comes earlier, and is

then written in memory.

9

1063CS–CBIC–01/03