GT28F160F3B120 데이터 시트보기 (PDF) - Intel

부품명

상세내역

제조사

GT28F160F3B120 Datasheet PDF : 47 Pages

| |||

FAST BOOT BLOCK DATASHEET

E

Sym

A0–A19

DQ0–

DQ15

CLK

ADV#

CE#

RST#

OE#

WE#

WP#

WAIT#

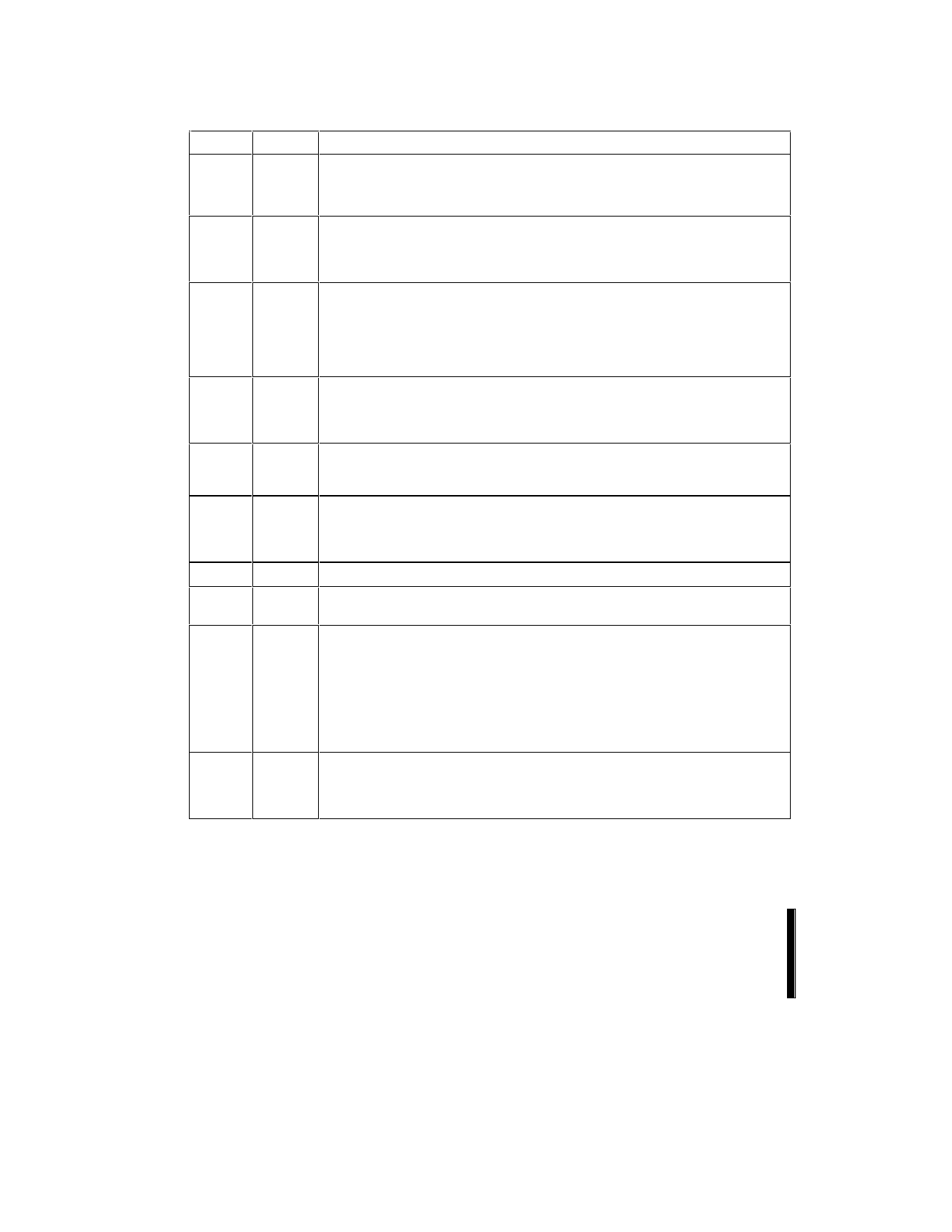

Table 1. Pin Descriptions

Type

Name and Function

INPUT ADDRESS INPUTS: Inputs for addresses during read and write operations.

Addresses are internally latched during read and write cycles.

8-Mbit: A0–18, 16-Mbit: A0–19

INPUT/

OUTPUT

DATA INPUT/OUTPUTS: Inputs data and commands during write cycles, outputs

data during memory array, status register (DQ0–DQ7), and identifier code read

cycles. Data pins float to high-impedance when the chip is deselected or outputs

are disabled. Data is internally latched during a write cycle.

INPUT

CLOCK: Synchronizes the flash memory to the system operating frequency during

synchronous burst-mode read operations. When configured for synchronous burst-

mode reads, address is latched on the first rising (or falling, depending upon the

read configuration register setting) CLK edge when ADV# is active or upon a rising

ADV# edge, whichever occurs first. CLK is ignored during asynchronous page-

mode read and write operations.

INPUT

ADDRESS VALID: Indicates that a valid address is present on the address inputs.

Addresses are latched on the rising edge of ADV# during read and write

operations. ADV# may be tied active during asynchronous read and write

operations.

INPUT

CHIP ENABLE: Activates the device’s control logic, input buffers, decoders, and

sense amplifiers. CE#-high deselects the device and reduces power consumption

to standby levels.

INPUT

RESET: When driven low, RST# inhibits write operations which provides data

protection during power transitions, and it resets internal automation. RST#-high

enables normal operation. Exit from reset sets the device to asynchronous read

array mode.

INPUT OUTPUT ENABLE: Gates data outputs during a read cycle.

INPUT WRITE ENABLE: Controls writes to the CUI and array. Addresses and data are

latched on the rising edge of the WE# pulse.

INPUT WRITE PROTECTION: Provides a method for locking and unlocking all main

blocks and two parameter blocks.

When WP# is at logic low, lockable blocks are locked. If a program or erase

operation is attempted on a locked block, SR.1 and either SR.4 [program] or SR.5

[block erase] will be set to indicate the operation failed.

When WP# is at logic high, the lockable blocks are unlocked and can be

programmed or erased.

OUTPUT

WAIT: Provides data valid feedback when configured for synchronous burst-mode

and the burst length is set to continuous. This signal is gated by OE# and CE# and

is internally pull-up to VCCQ via a resistor. WAIT# from several components can be

tied together to form one system WAIT# signal.

8

PRODUCT PREVIEW