IMC010FLSA-15 데이터 시트보기 (PDF) - Intel

부품명

상세내역

제조사

IMC010FLSA-15 Datasheet PDF : 39 Pages

| |||

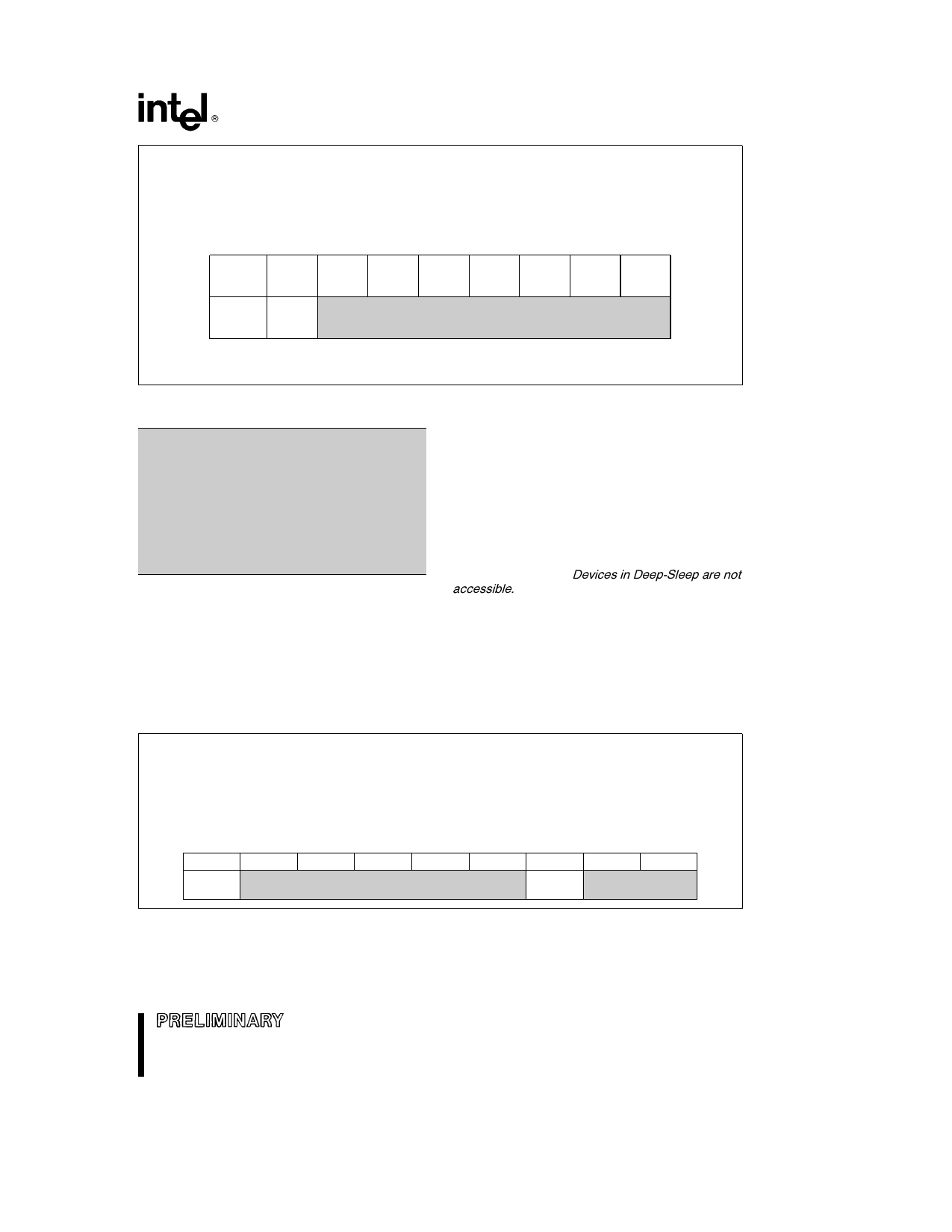

SERIES 2 FLASH MEMORY CARDS

SOFT RESET REGISTER

(CONFIGURATION OPTION REGISTER)

(Read Write Register)

ADDRESS BIT 7

BIT 6

BIT 5

BIT 4

BIT 4

BIT 2

BIT 1

BIT 0

4000H SRESET

PCMCIA CONFIGURATION INDEX

RESETS TO ZERO ON POWER UP

1 e RESET CLEAR TO ACCESS CARD

Figure 5 SOFT RESET REGISTER (PCMCIA) Sets the Memory Card in the Power-On Default State

POWER-ON DEFAULT CONDITIONS

All Devices Powered Up In Standby Mode

Common Memory Available For Writes

All Device Ready Busy Outputs Unmasked

PCMCIA Ready Busy Mode Enabled

Ready Busy Output Goes To Ready

Global PowerDown Register (PCMCIA)

(Configuration and Status)

The Global Reset-PowerDown Register (Attribute

Memory Plane Address 4002H Figure 6) is referred

to as the Configuration and Status Register in the

PCMCIA Release 2 0 specification

Bit 2 (RP) controls global card power-down Writing

a 1 to this bit places each device within the card into

‘‘Deep-Sleep’’ mode Devices in Deep-Sleep are not

accessible Recovery from power-down requires

500 ns for reads and 1 ms for writes

The RP bit defaults to 0 on card power-up or reset

Setting or clearing this bit has no affect on the bit

settings of the Sleep Control Register

The remaining Global Reset-PwrDwn Register bits

are defined for Intel’s family of I O cards and are

driven low for compatibility

ADDRESS

4002H

GLOBAL RESET-POWER-DOWN REGISTER

(CONFIGURATION AND STATUS REGISTER)

(Read Write Register)

BIT 7

BIT 6

BIT 5

BIT 4

1 e POWER DOWN

BIT 3

BIT 2

BIT 1

BIT 0

ZEROES

RP

ZEROES

Figure 6 GLOBAL RESET-PWRDWN REGISTER (PCMCIA) The RP

Bit Enables Reset PowerDown of All Flash Memory Devices

11