OR4E10 데이터 시트보기 (PDF) - Agere -> LSI Corporation

부품명

상세내역

제조사

OR4E10 Datasheet PDF : 124 Pages

| |||

Preliminary Data Sheet

December 2000

ORCA Series 4 FPGAs

System Features (continued)

s Variable-size bused readback of configuration data capability with the built-in MPI and system bus.

s Internal, 3-state, bidirectional buses with simple control provided by the SLIC.

s Meets universal test and operations PHY interface for ATM (UTOPIA) Levels 1, 2, and 3. Also meets proposed

specifications for UTOPIA Level 4 for 10 Gbits/s interfaces.

s New clock routing structures for global and local clocking significantly increases speed and reduces skew

(<200 ps for OR4E4).

s New local clock routing structures allow creation of localized clock trees anywhere on the device.

s New DDR, QDR, and ZBT memory interfaces support the latest high-speed memory interfaces.

s New 2x/4x uplink and downlink I/O shift registers capabilities interface high-speed external I/Os to reduced inter-

nal logic speed.

s ORCA Foundry 2000 development system software. Supported by industry-standard CAE tools for design entry,

synthesis, simulation, and timing analysis.

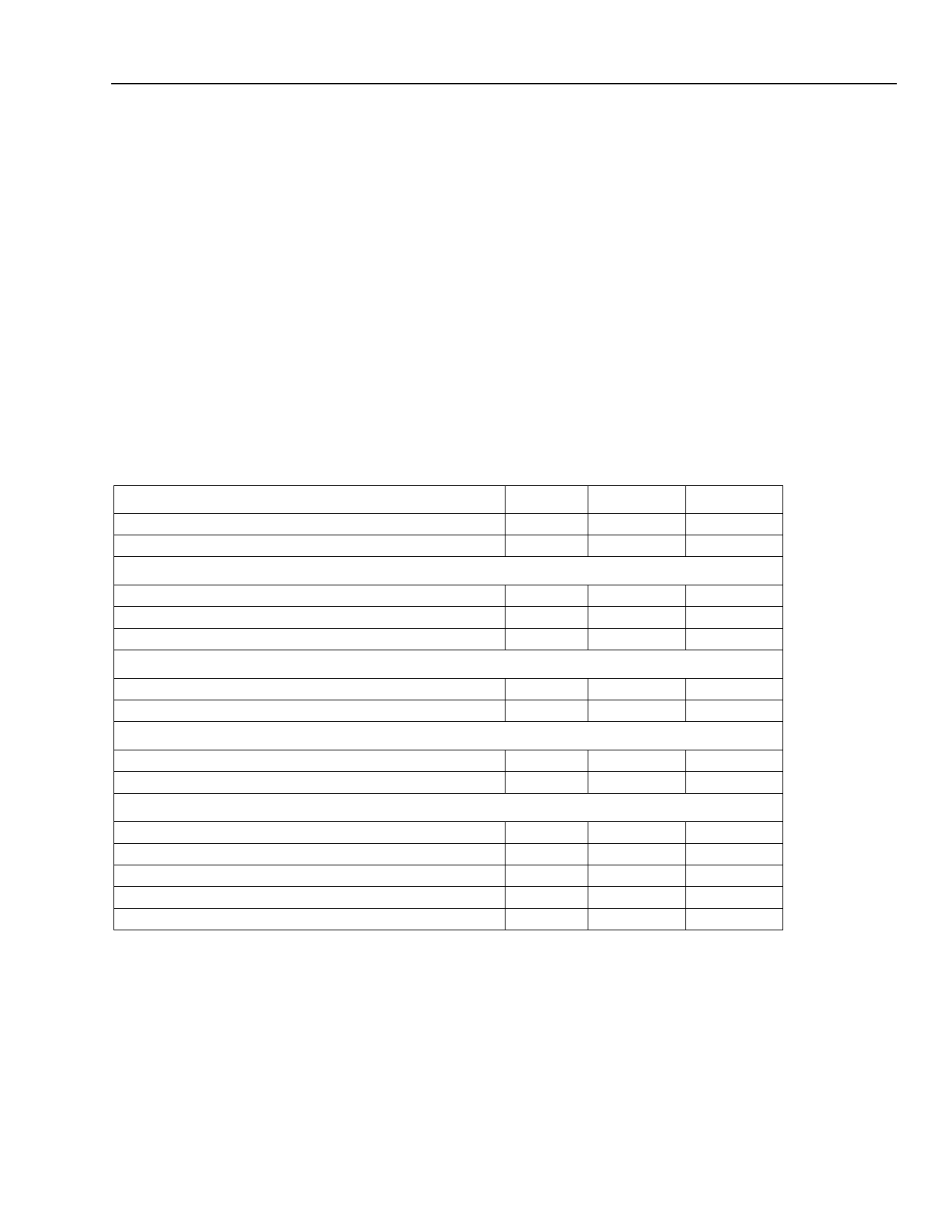

Table 2. System Performance

Function

16-bit loadable up/down counter

16-bit accumulator

8 x 8 Parallel Multiplier

Multiplier mode, unpipelined 1

ROM mode, unpipelined 2

Multiplier mode, pipelined 3

32 x 16 RAM (synchronous)

Single port, 3-state bus 4

Dual-port 5

128 x 8 RAM (synchronous)

Single port, 3-state bus 4

Dual-port, 3-state bus 5

Address Decode

8-bit internal, LUT-based

8-bit internal, SLIC-based 6

32-bit internal, LUT-based

32-bit internal, SLIC-based 7

36-bit Parity Check (internal)

No. PFUs

2

2

282

2

282

11.5

72

8

175

15

197

4

264

4

340

8

264

8

264

0.25

1.37

0

0.73

2

4.68

0

2.08

2

4.68

Unit

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

ns

ns

ns

ns

ns

1. Implemented using 8 x 1 multiplier mode (unpipelined), register-to-register, two 8-bit inputs, one 16-bit output.

2. Implemented using two 32 x 4 RAMs and one 12-bit adder, one 8-bit input, one fixed operand, one 16-bit output.

3. Implemented using 8 x 1 multiplier mode (fully pipelined), two 8-bit inputs, one 16-bit output (seven of 15 PFUs

contain only pipelining registers).

4. Implemented using 32 x 4 RAM mode with read data on 3-state buffer to bidirectional read/write bus.

5. Implemented using 32 x 4 dual-port RAM mode.

6. Implemented in one partially occupied SLIC, with decoded output setup to CE in the same PLC.

7. Implemented in five partially occupied SLICs.

Lucent Technologies Inc.

5