M80C186EB-13 데이터 시트보기 (PDF) - Intel

부품명

상세내역

제조사

M80C186EB-13 Datasheet PDF : 56 Pages

| |||

M80C186EB

INSTRUCTION SET

The instruction set is divided into seven categories

data transfer arithmetic shift rotate logical string

manipulation control transfer high-level instruc-

tions and processor control These categories are

summarized in Figure 4

An M80C186EB instruction can reference anywhere

from zero to several operands An operand can

reside in a register in the instruction itself or in

memory

MEMORY ORGANIZATION

Memory is organized in sets of segments Each seg-

ment is a linear contiguous sequence of up to 64K

(216) 8-bit bytes Memory is addressed using a two-

component address (a pointer) that consists of a

16-bit base segment and a 16-bit offset The 16-bit

base segment values are contained in one of four

internal segment registers (code data stack extra)

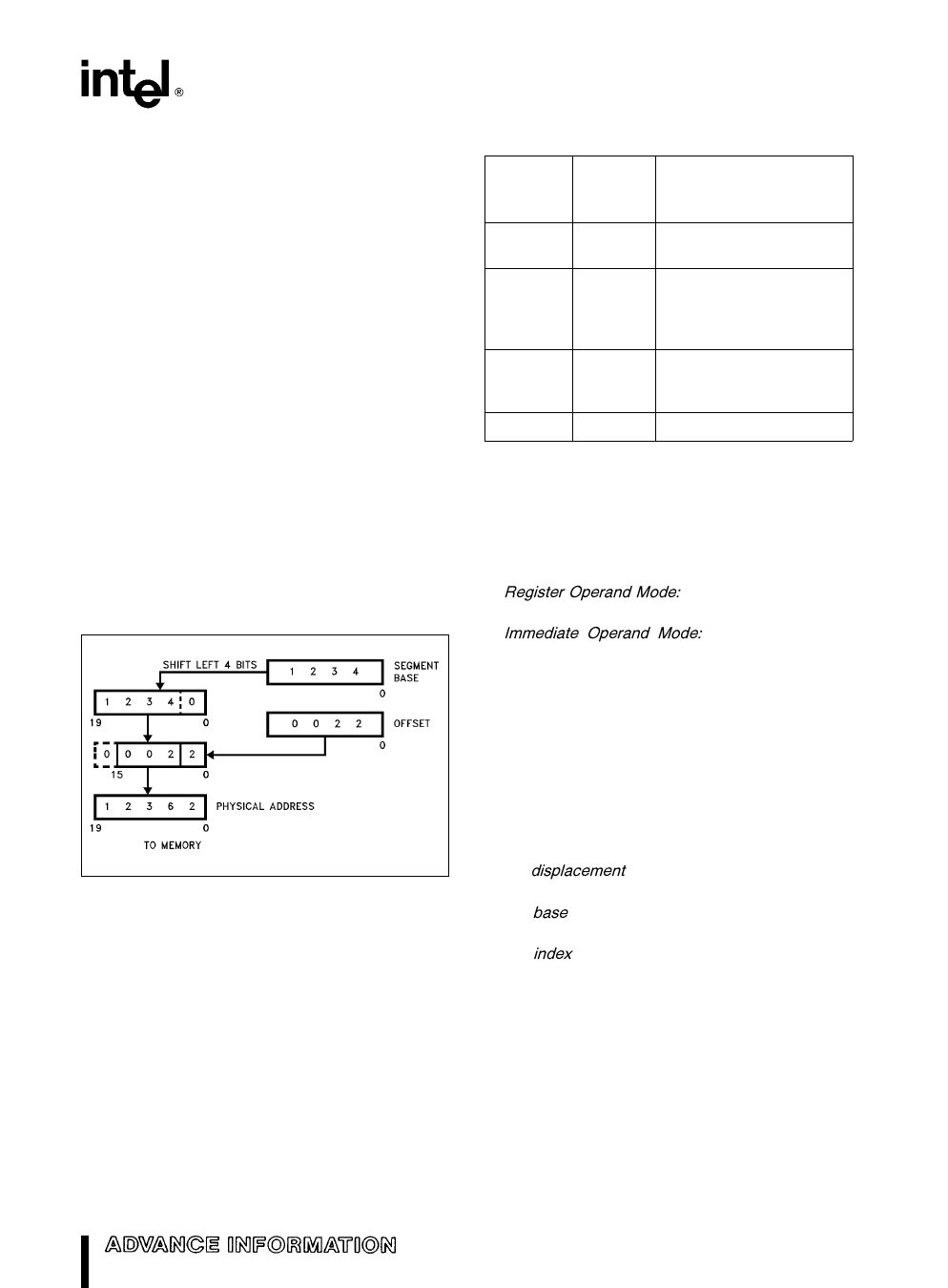

The physical address is calculated by shifting the

base value left by four bits and adding the 16-bit

offset value to yield a 20-bit physical address (see

Figure 3) The resulting 20-bit address allows for a

1 Mbyte address range

271214 –3

Figure 3 Two Component Address

All instructions that address operands in memory

must specify the base segment and the 16-bit offset

value For speed and compact instruction encoding

the segment register used for a physical address

generation is implied by the addressing mode used

(see Table 1) Special segment override instruction

prefixes allow the implicit segment register selection

rules to be overridden for special cases The code

stack data and extra segments may coincide for

simple programs

Table 1 Segment Register Selection Rules

Memory Segment

Reference Register

Needed Used

Implicit Segment

Selection Rule

Instructions Code (CS) Instruction prefetch and

immediate data

Stack

Stack (SS) All stack pushes and pops

any memory references

which use the BP register

as a base

External Extra (ES) All String instruction

references which use the

DI register as an index

Local Data Data (DS) All other data references

ADDRESSING MODES

The M80C186EB provides eight categories of ad-

dressing modes to specify operands Two address-

ing modes are provided for instructions that operate

on register or immediate operands

Register Operand Mode The operand is located

in one of the 8- or 16-bit general registers

Immediate Operand Mode The operand is in-

cluded in the instruction

Six modes are provided to specify the location of an

operand in a memory segment A memory operand

address consists of two 16-bit components a seg-

ment base and an offset The segment base is sup-

plied by a 16-bit segment register either implicitly

chosen by the addressing mode or explicitly chosen

by a segment override prefix The offset also called

the effective address is calculated by summing any

combination of the following three address ele-

ments

the displacement (an 8- or 16-bit immediate value

contained in the instruction)

the base (contents of either the BX or BP base

registers) and

the index (contents of either the SI or DI index

registers)

5