7805ALPRPFB 데이터 시트보기 (PDF) - MAXWELL TECHNOLOGIES

부품명

상세내역

제조사

7805ALPRPFB Datasheet PDF : 22 Pages

| |||

16-Bit Latchup Protected Analog to Digital Converter 7809LP

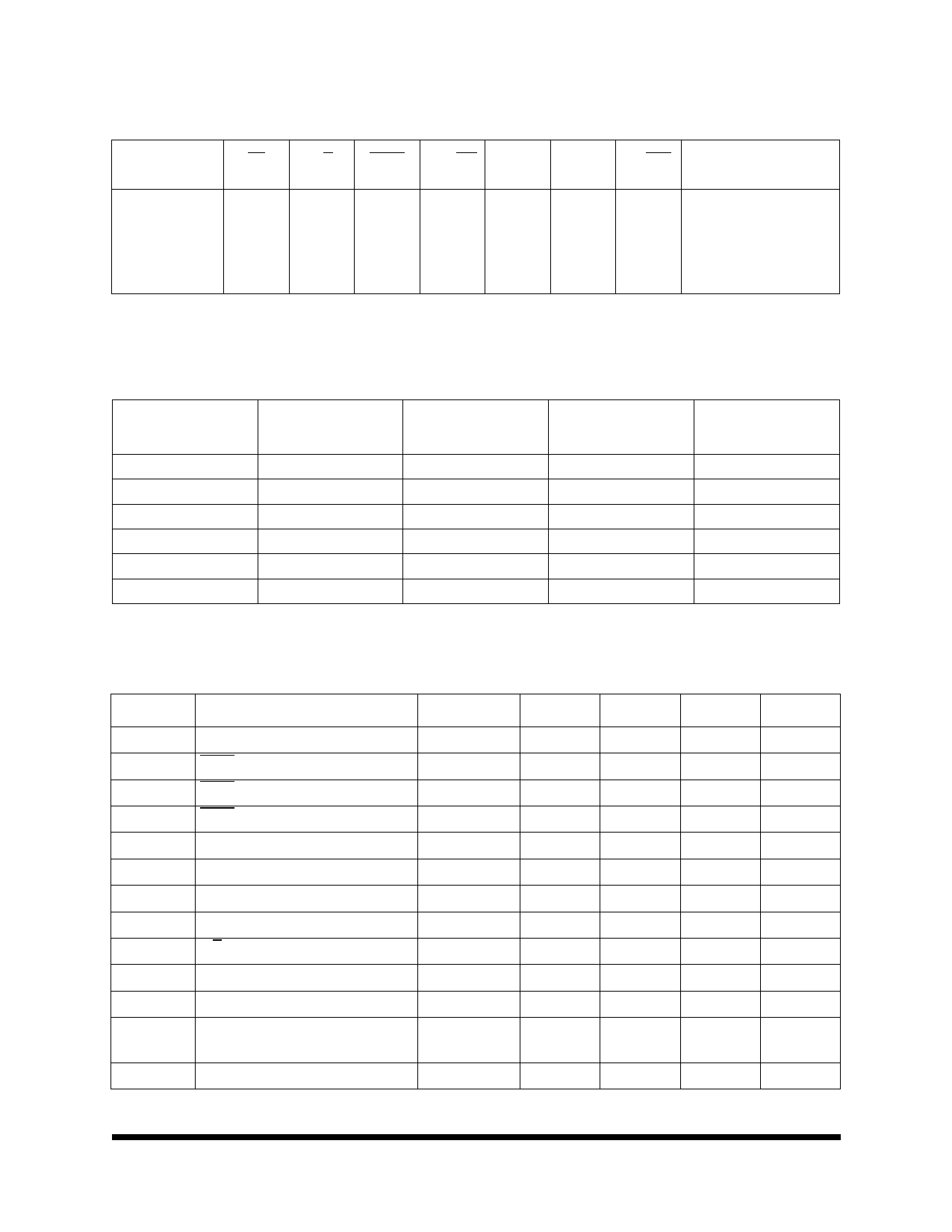

TABLE 12. 7809LP CONTROL LINE FUNCTIONS FOR READ AND CONVERT

SPECIFIC FUNCTION

CS

R/C

BUSY

EXT/INT

DATACL

K

PWRD

SB/BTC OPERATION

Selecting Output

x

x

x

x

x

x

0 Serial data is output in

Format

3 Binary Two’s Comple-

x

x

x

x

x

x

1 ment format.

Serial data is output in

Straight Binary format.

1. See Figure 4 for constraints on previous data valid during conversion.

ANALOG INPUT RANGE

± 10V

± 5V

±3.3V

0V to 10V

0V to 5V

0V to 4V

TABLE 13. 7809LP INPUT RANGE CONNECTION

CONNECT R1IN VIA 200Ω CONNECT R2IN VIA 100Ω

TO

TO

CONNECT R3IN TO

VIN

AGND

VIN

AGND

AGND

VIN

AGND

VIN

VIN

VIN

AGND

AGND

CAP

CAP

CAP

AGND

VIN

VIN

IMPEDANCE

22.9 kΩ

13.3 kΩ

10.7 kΩ

13.3kΩ

10.0 kΩ

10.7 kΩ

TABLE 14. 7809LP CONVERSION AND DATA TIMING

(TA = -40 °C TO 85 °C UNLESS OTHERWISE SPECIFIED)

SYMBOL DESCRIPTION

SUBGROUPS

MIN

TYP

MAX

UNIT

t1

Convert Pulse Width

9, 10, 11

40

--

6000

ns

t2

BUSY Delay

9, 10, 11

--

--

65

ns

t3

BUSY LOW

9, 10, 11

--

--

8

µs

t4

BUSY Delay after End of Conversion 9, 10, 11

--

220

--

ns

t5

Aperture Delay

9, 10, 11

--

40

--

ns

t6

Conversion Time

9, 10, 11

--

7.6

8

µs

t7

Acquisition Time

9, 10, 11

--

--

2

µs

t6 + t7 Throughput Time

9, 10, 11

--

9

10

µs

t8

R/C Low to DATACLK Delay

9, 10, 11

--

450

--

ns

t9

DATACLK Period

9, 10, 11

--

440

--

ns

t10

Data Valid to DATACLK HIGH Delay

9, 10, 11

20

75

--

ns

t11 Data Valid after DATACLK LOW

9, 10, 11

100

125

--

ns

Delay

t12 External DATACLK

9, 10, 11

100

--

--

ns

01.11.05 Rev 7

All data sheets are subject to change without notice 8

©2005 Maxwell Technologies

All rights reserved.