X24164P 데이터 시트보기 (PDF) - Xicor -> Intersil

부품명

상세내역

제조사

X24164P Datasheet PDF : 14 Pages

| |||

X24164

READ OPERATIONS

Read operations are initiated in the same manner as write

operations with the exception that the R/W bit of the slave

address is set to a one. There are three basic read

operations: current address read, random read and se-

quential read.

It should be noted that the ninth clock cycle of the read

operation is not a “don’t care.” To terminate a read

operation, the master must either issue a stop condition

during the ninth cycle or hold SDA HIGH during the ninth

clock cycle and then issue a stop condition.

Current Address Read

Internally the X24164 contains an address counter that

maintains the address of the last word accessed,

incremented by one. Therefore, if the last access (either

a read or write) was to address n, the next read operation

would access data from address n + 1. Upon receipt of

the slave address with the R/W set to one, the X24164

issues an acknowledge and transmits the eight bit word.

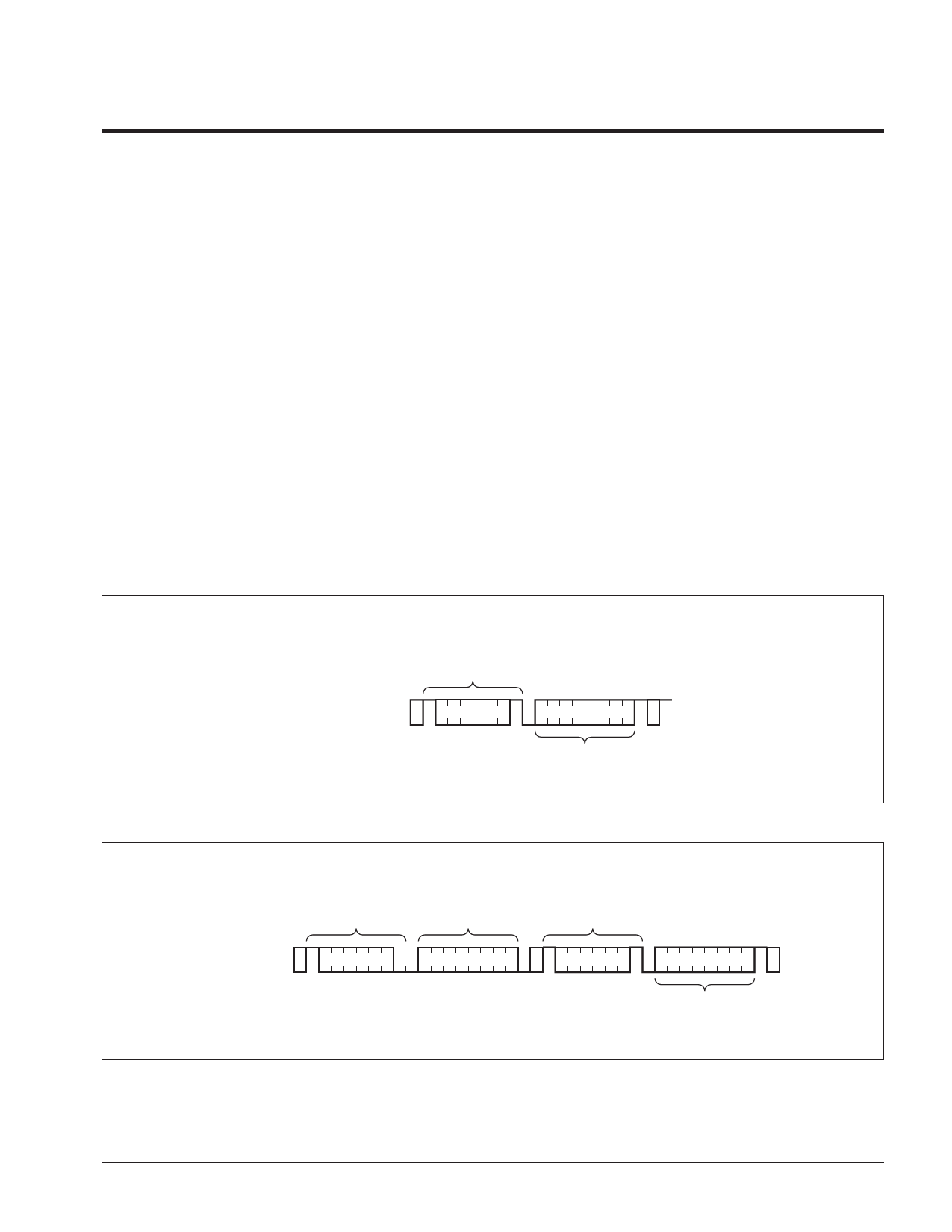

Figure 7. Current Address Read

The read operation is terminated by the master; by not

responding with an acknowledge and by issuing a stop

condition. Refer to Figure 7 for the sequence of address,

acknowledge and data transfer.

Random Read

Random read operations allow the master to access any

memory location in a random manner. Prior to issuing

the slave address with the R/W bit set to one, the master

must first perform a “dummy” write operation. The mas-

ter issues the start condition, and the slave address

followed by the word address it is to read. After the word

address acknowledge, the master immediately reissues

the start condition and the slave address with the R/W bit

set to one. This will be followed by an acknowledge from

the X24164 and then by the eight bit word. The read

operation is terminated by the master; by not responding

with an acknowledge and by issuing a stop condition.

Refer to Figure 8 for the address, acknowledge and data

transfer sequence.

S

T

BUS ACTIVITY: A

MASTER

R

SLAVE

ADDRESS

S

T

O

T

P

SDA LINE

S

P

BUS ACTIVITY:

X24164

A

C

K

DATA

Figure 8. Random Read

3846 FHD F14

S

T

BUS ACTIVITY: A

MASTER

R

T

SLAVE

ADDRESS

WORD

ADDRESS n

S

T

A

R

SLAVE

ADDRESS

T

SDA LINE

S

S

BUS ACTIVITY:

X24164

A

A

A

C

C

C

K

K

K

DATA n

S

T

O

P

P

3846 FHD F15

7