AB28F800BR-T80 데이터 시트보기 (PDF) - Intel

부품명

상세내역

제조사

AB28F800BR-T80 Datasheet PDF : 36 Pages

| |||

A28F200BR

E

1.5 Pin Descriptions

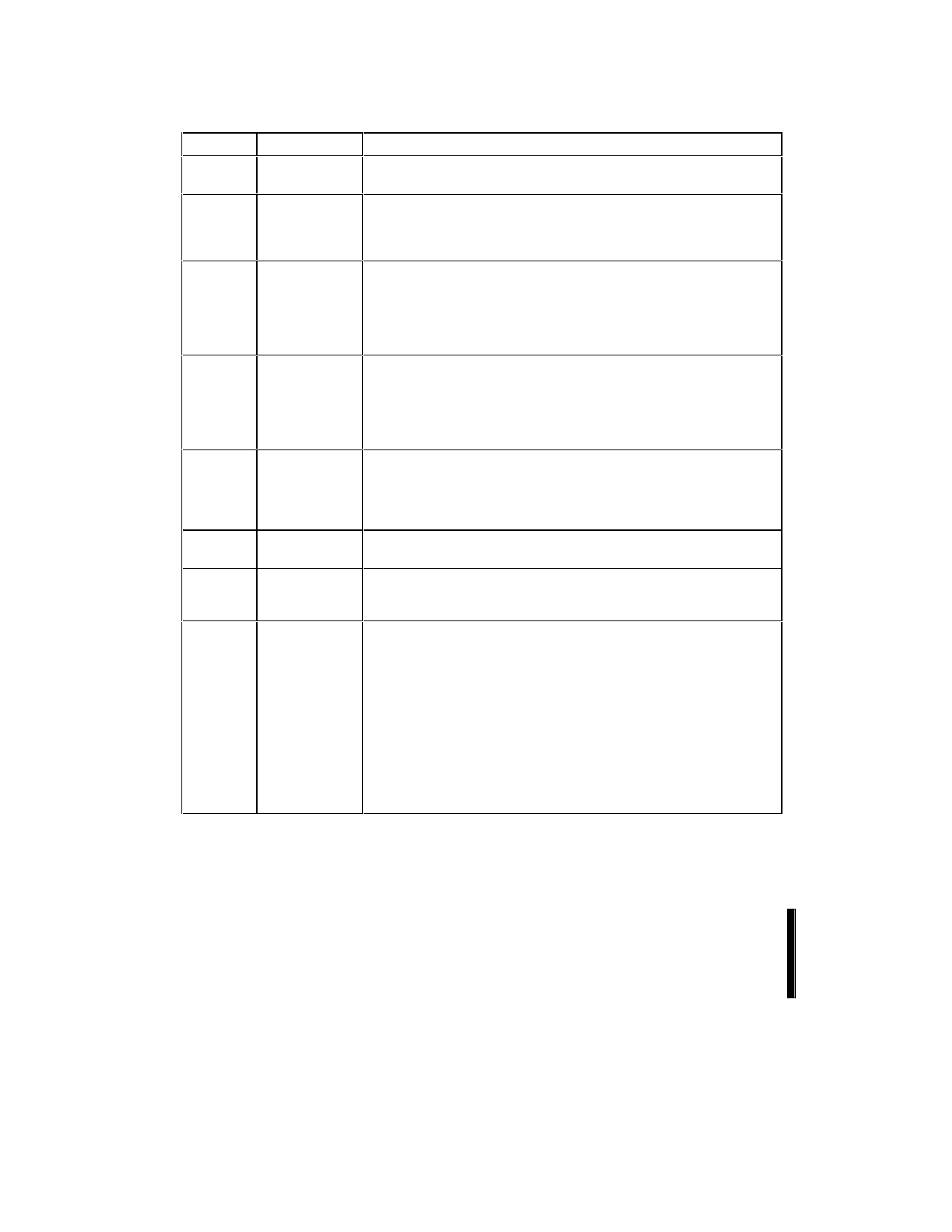

Table 1. 28F200 Pin Descriptions

Symbol

Type

Name and Function

A0 - A16

INPUT

ADDRESS INPUTS for memory addresses. Addresses are internally

latched during a write cycle.

A9

INPUT

ADDRESS INPUT: When A9 is at VHH the signature mode is accessed.

During this mode, A0 decodes between the manufacturer and device IDs.

When BYTE# is at a logic low, only the lower byte of the signatures are

read. DQ15/A-1 is a don’t care in the signature mode when BYTE# is low.

DQ0-DQ7

INPUT/OUTPUT

DATA INPUTS/OUTPUTS: Inputs array data on the second CE# and

WE# cycle during a Program command. Inputs commands to the

Command User Interface when CE# and WE# are active. Data is

internally latched during the Write cycle. Outputs array, Intelligent

Identifier and Status Register data. The data pins float to tri-state when

the chip is de-selected or the outputs are disabled.

DQ8-DQ15

INPUT/OUTPUT

DATA INPUTS/OUTPUTS: Inputs array data on the second CE# and

WE# cycle during a Program command. Data is internally latched during

the Write cycle. Outputs array data. The data pins float to tri-state when

the chip is de-selected or the outputs are disabled as in the byte-wide

mode (BYTE# = “0”). In the byte-wide mode DQ15/A-1 becomes the lowest

order address for data output on DQ0-DQ7.

CE#

INPUT

CHIP ENABLE: Activates the device’s control logic, input buffers,

decoders and sense amplifiers. CE# is active low. CE# high de-selects

the memory device and reduces power consumption to standby levels. If

CE# and RP# are high, but not at a CMOS high level, the standby current

will increase due to current flow through the CE# and RP# input stages.

OE#

INPUT

OUTPUT ENABLE: Enables the device’s outputs through the data buffers

during a read cycle. OE# is active low.

WE#

INPUT

WRITE ENABLE: Controls writes to the Command Register and array

blocks. WE# is active low. Addresses and data are latched on the rising

edge of the WE# pulse.

RP#

INPUT

RESET/DEEP POWER-DOWN: Uses three voltage levels (VIL, VIH, and

VHH) to control two different functions: reset/deep power-down mode and

boot block unlocking. It is backwards-compatible with the 28F200BX/BL.

When RP# is at logic low, the device is in reset/deep power-down

mode, which puts the outputs at High-Z, resets the Write State Machine,

and draws minimum current.

When RP# is at logic high, the device is in standard operation. When

RP# transitions from logic-low to logic-high, the device defaults to the

read array mode.

When RP# is at VHH, the boot block is unlocked and can be

programmed or erased. This overides any control from the WP# input.

8

ADVANCE INFORMATION