AB28F800BR-B80 데이터 시트보기 (PDF) - Intel

부품명

상세내역

제조사

AB28F800BR-B80 Datasheet PDF : 36 Pages

| |||

E

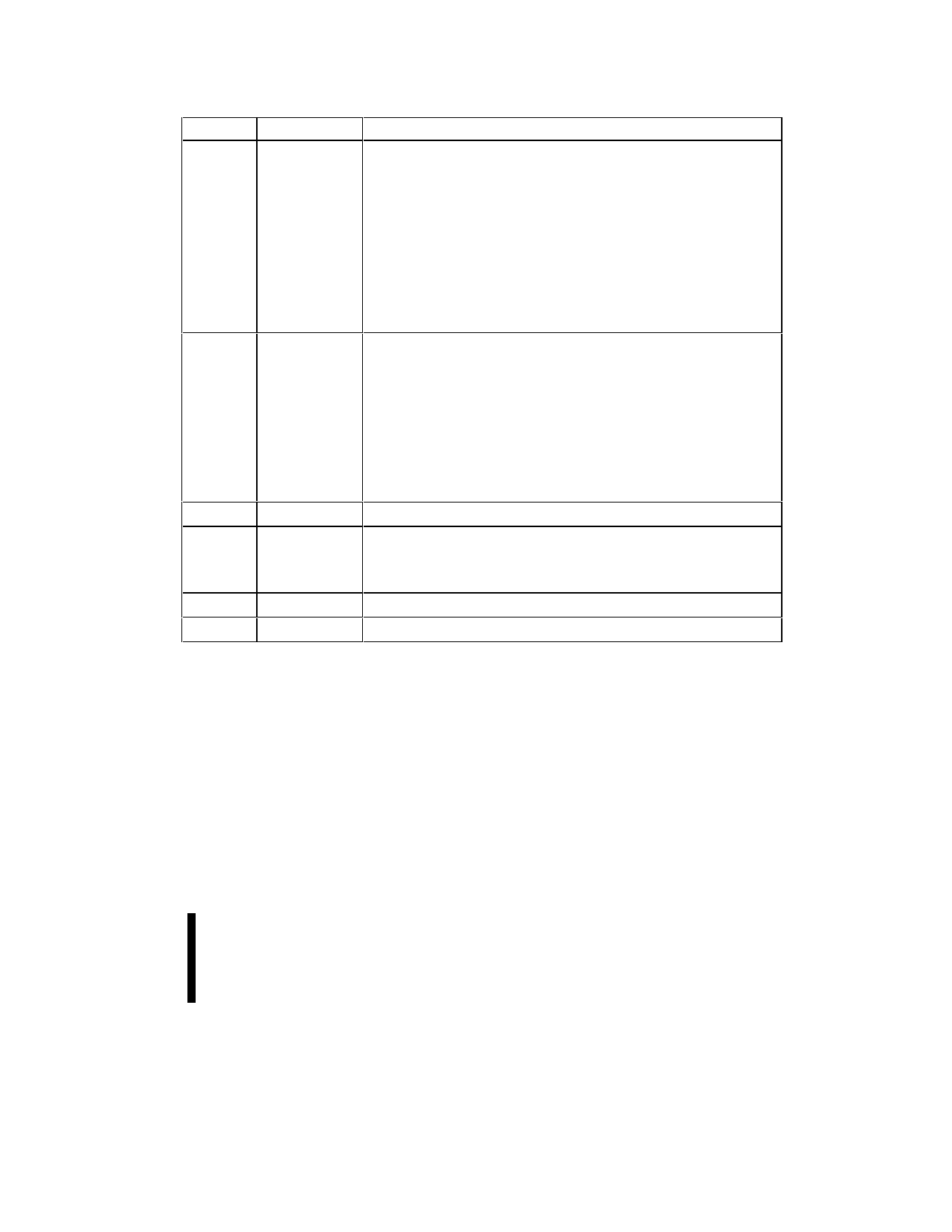

Symbol

WP#

Type

INPUT

BYTE#

INPUT

VCC

VPP

GND

NC

A28F200BR

Table 1. 28F200 Pin Descriptions (Continued)

Name and Function

WRITE PROTECT: Provides a method for unlocking the boot block in a

system without a 12V supply.

When WP# is at logic low, the boot block is locked, preventing

program and erase operations to the boot block. If a program or erase

operation is attempted on the boot block when WP# is low, the

corresponding status bit (bit 4 for program, bit 5 for erase) will be set in

the Status Register to indicate the operation failed.

When WP# is at logic high, the boot block is unlocked and can be

programmed or erased.

NOTE: This feature is overridden and the boot block unlocked when RP#

is at VHH. See Section 3.4 for details on write protection.

BYTE# ENABLE: Controls whether the device operates in the byte-wide

(x8) mode or the word (x16) mode. The BYTE# input must be controlled

at CMOS levels to meet the CMOS current specification in the standby

mode.

When BYTE# is at logic low, the byte-wide mode is enabled. A 19-bit

address is applied on A-1 to A17, and 8 bits of data is read and written on

DQ0-DQ7.

When BYTE# is at logic high, the word-wide mode is enable. An 18-bit

address is applied on A0 to A17 and 16 bits of data is read and written on

DQ0 - DQ15.

DEVICE POWER SUPPLY: 5.0V ± 10%

PROGRAM/ERASE POWER SUPPLY: For erasing memory array blocks

or programming data in each block, a voltage either of 5V ± 10% or 12V ±

5% must be applied to this pin. When VPP < VPPLK all blocks are locked

and protected against Program and Erase commands.

GROUND: For all internal circuitry.

NO CONNECT: Pin may be driven or left floating.

2.0 PRODUCT DESCRIPTON

2.1 Memory Blocking Organization

This product family features an asymmetrically-

blocked architecture enhancing system memory

integration. Each block can be erased

independently of the others up to 10,000 times. The

block sizes have been chosen to optimize their

functionality for common applications of nonvolatile

storage. For the address locations of the blocks,

see the memory maps in Figure 3.

2.1.1

ONE 16-KB BOOT BLOCK

The boot block is intended to replace a dedicated

boot PROM in a microprocessor or microcontroller-

based system. The 16-Kbyte (16,384 bytes) boot

block is located at either the top (denoted by -T

suffix) or the bottom (-B suffix) of the address map

to accommodate different microprocessor protocols

for boot code location. This boot block features

hardware controllable write-protection to protect the

crucial microprocessor boot code from accidental

erasure. The protection of the boot block is

controlled using a combination of the VPP, RP#, and

WP# pins, as is detailed in Table 8.

ADVANCE INFORMATION

9