24AA32A-24LC32A 데이터 시트보기 (PDF) - Microchip Technology

부품명

상세내역

제조사

24AA32A-24LC32A Datasheet PDF : 26 Pages

| |||

24AA32A/24LC32A

6.0 READ OPERATION

Read operations are initiated in the same way as write

operations, with the exception that the R/W bit of the

control byte is set to ‘1’. There are three basic types of

read operations: current address read, random read,

and sequential read.

6.1 Current Address Read

The 24XX32A contains an address counter that main-

tains the address of the last word accessed, internally

incremented by ‘1’. Therefore, if the previous read

access was to address n (n is any legal address), the

next current address read operation would access data

from address n + 1.

Upon receipt of the control byte with R/W bit set to ‘1’,

the 24XX32A issues an acknowledge and transmits the

8- bit data word. The master will not acknowledge the

transfer but does generate a Stop condition and the

24XX32A discontinues transmission (Figure 6-1).

6.2 Random Read

Random read operations allow the master to access

any memory location in a random manner. To perform

this type of read operation, the word address must

first be first. This is accomplished by sending the word

address to the 24XX32A as part of a write operation

(R/W bit set to ‘0’). Once the word address is sent, the

master generates a Start condition following the

acknowledge. This terminates the write operation, but

not before the internal address pointer is set. The

master issues the control byte again, but with the R/W

bit set to a ‘1’. The 24XX32A will then issue an

acknowledge and transmit the 8-bit data word. The

master will not acknowledge the transfer but does

generate a Stop condition which causes the 24XX32A

to discontinue transmission (Figure 6-2). After a ran-

dom Read command, the internal address counter will

point to the address location following the one that

was just read.

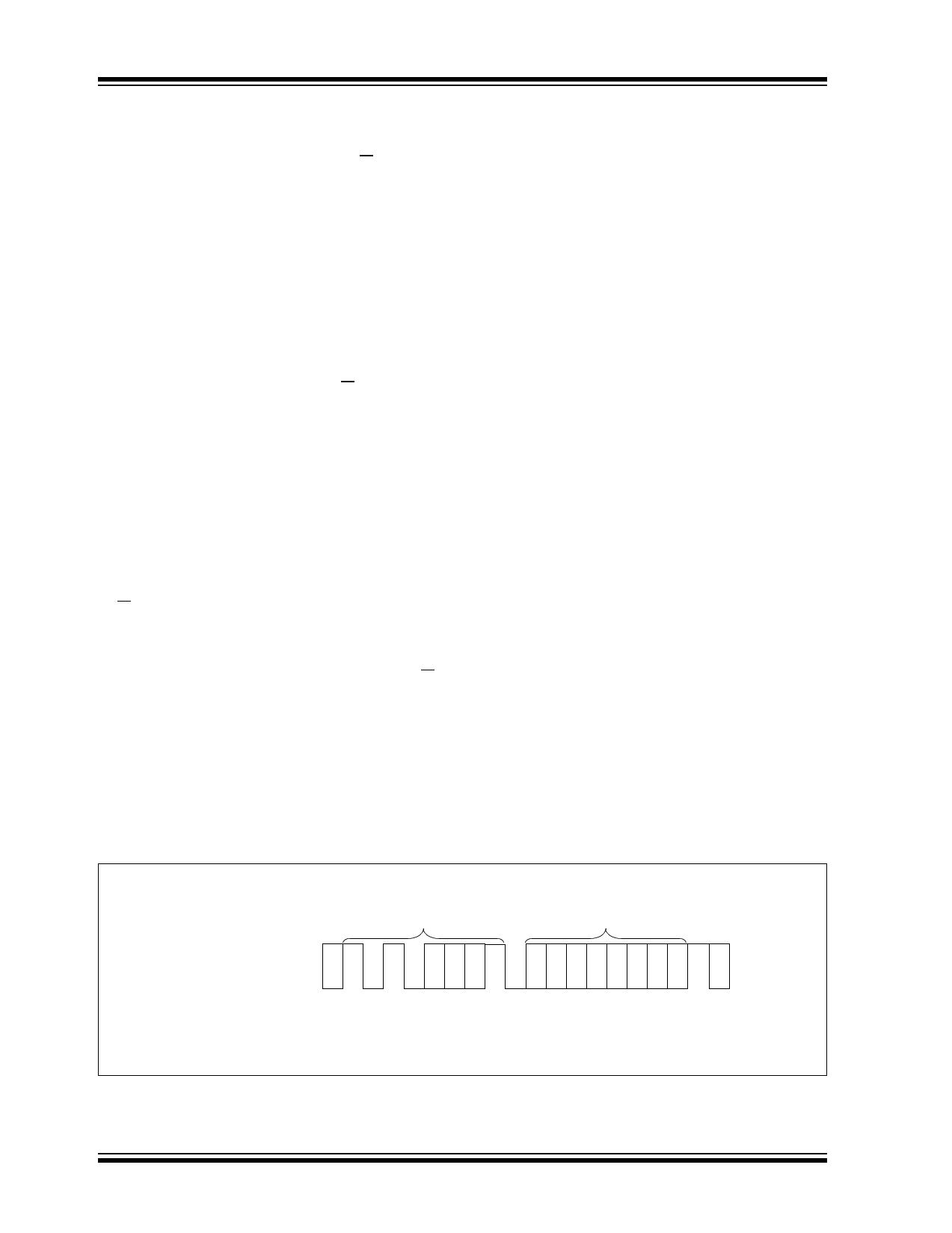

FIGURE 6-1:

CURRENT ADDRESS READ

S

BUS ACTIVITY T

MASTER

A

R

T

CONTROL

BYTE

SDA LINE

S

BUS ACTIVITY

6.3 Sequential Read

Sequential reads are initiated in the same way as a

random read, except that once the 24XX32A transmits

the first data byte, the master issues an acknowledge

as opposed to the Stop condition used in a random

read. This acknowledge directs the 24XX32A to

transmit the next sequentially addressed 8-bit word

(Figure 6-3). Following the final byte transmitted to the

master, the master will NOT generate an acknowledge

but will generate a Stop condition. To provide sequen-

tial reads, the 24XX32A contains an internal address

pointer which is incremented by ‘1’ upon completion of

each operation. This address pointer allows the entire

memory contents to be serially read during one

operation. The internal address pointer will automati-

cally roll over from address FFF to address 0000 if the

master acknowledges the byte received from the array

address 0FFF.

DATA (n)

A

C

K

S

T

O

P

P

N

O

A

C

K

DS21713D-page 10

2003 Microchip Technology Inc.