28F016XD-85 데이터 시트보기 (PDF) - Intel

부품명

상세내역

제조사

28F016XD-85 Datasheet PDF : 54 Pages

| |||

E

28F016XD FLASH MEMORY

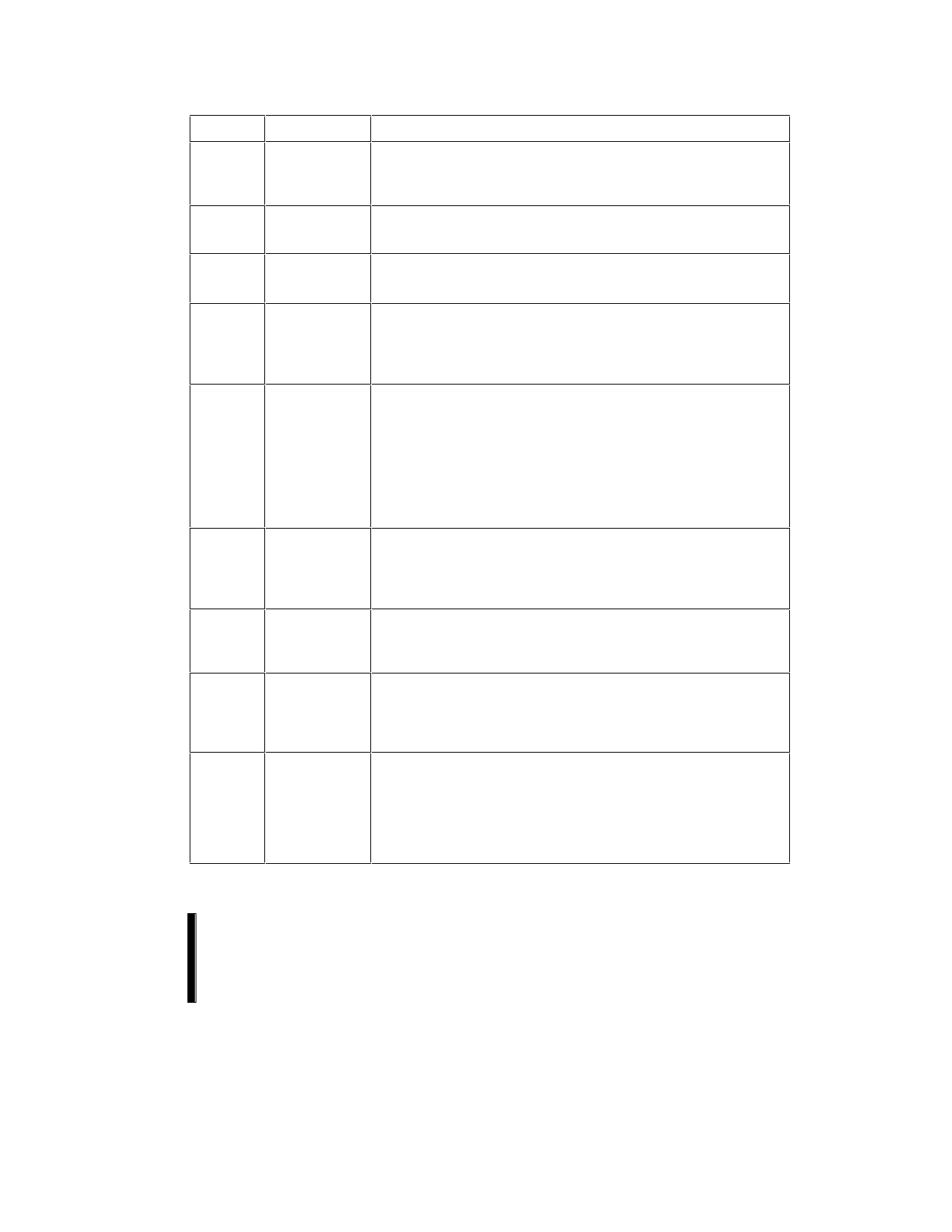

2.1 Lead Descriptions

Symbol

A0–A9

DQ0–DQ15

RAS#

CAS#

RP#

OE#

WE#

RY/BY#

WP#

Type

Name and Function

INPUT

INPUT/OUTPUT

INPUT

INPUT

INPUT

INPUT

INPUT

OPEN DRAIN

OUTPUT

INPUT

MULTIPLEXED ROW/COLUMN ADDRESSES: Selects a word within

one of thirty-two 32-Kword blocks. Row (upper) addresses are latched on

the falling edge of RAS#, while column (lower) addresses are latched on

the falling edge of CAS#.

DATA BUS: Inputs data and commands during CUI write cycles. Outputs

array, identifier or status data (DQ0-7) in the appropriate read mode.

Floated when the chip is de-selected or the outputs are disabled.

ROW ADDRESS STROBE: Latches row address information on inputs

A9-0 when RAS# transitions low. A subsequent CAS# low transition

initiates 28F016XD read or program operations.

COLUMN ADDRESS STROBE: Latches column address information on

inputs A9-0 when CAS# transitions low. When preceded by a RAS# low

transition, CAS# low initiates 28F016XD read or program operations,

along with OE# and WE#. Subsequent CAS# low transitions, with RAS#

held low, enable fast page mode reads/programs

RESET/POWER-DOWN: RP# low places the device in a deep power-

down state. All circuits that consume static power, even those circuits

enabled in standby mode, are turned off. When returning from deep

power-down, a recovery time of 300 ns at 5.0V VCC is required to allow

these circuits to power-up.

When RP# goes low, the current WSM operation is terminated, and the

device is reset. All Status Registers return to ready (with all status flags

cleared).

Exit from deep power-down places the device in read array mode.

OUTPUT ENABLE: Gates device data through the output buffers when

low in combination with RAS# and CAS# low. The outputs float to tri-state

off when OE# is high. OE# can be tied to GND if not controlled by the

system memory controller. RAS# and CAS# high override OE# low. WE#

low also overrides OE# low.

WRITE ENABLE: Controls access to the CUI, Data Register and Address

Register. WE# is active low and initiates programs in combination with

RAS# and CAS# low. WE# low overrides OE# low. RAS# and CAS# high

override WE# low.

READY/BUSY: Indicates status of the internal WSM. When low, it

indicates that the WSM is busy performing an operation. RY/BY# floating

indicates that the WSM is ready for new operations, erase is suspended,

or the device is in deep power-down mode. This output is always active

(i.e., not floated to tri-state off when OE#, RAS# or CAS# are high).

WRITE PROTECT: Erase blocks can be locked by writing a nonvolatile

lock-bit for each block. When WP# is low, those locked blocks as

reflected by the Block-Lock Status bits (BSR.6), are protected from

inadvertent data programs or erases. When WP# is high, all blocks can

be written or erased regardless of the state of the lock-bits. The WP#

input buffer is disabled when RP# transitions low (deep power-down

mode).

9