RTL8208 데이터 시트보기 (PDF) - Realtek Semiconductor

부품명

상세내역

제조사

RTL8208 Datasheet PDF : 40 Pages

| |||

RTL8208

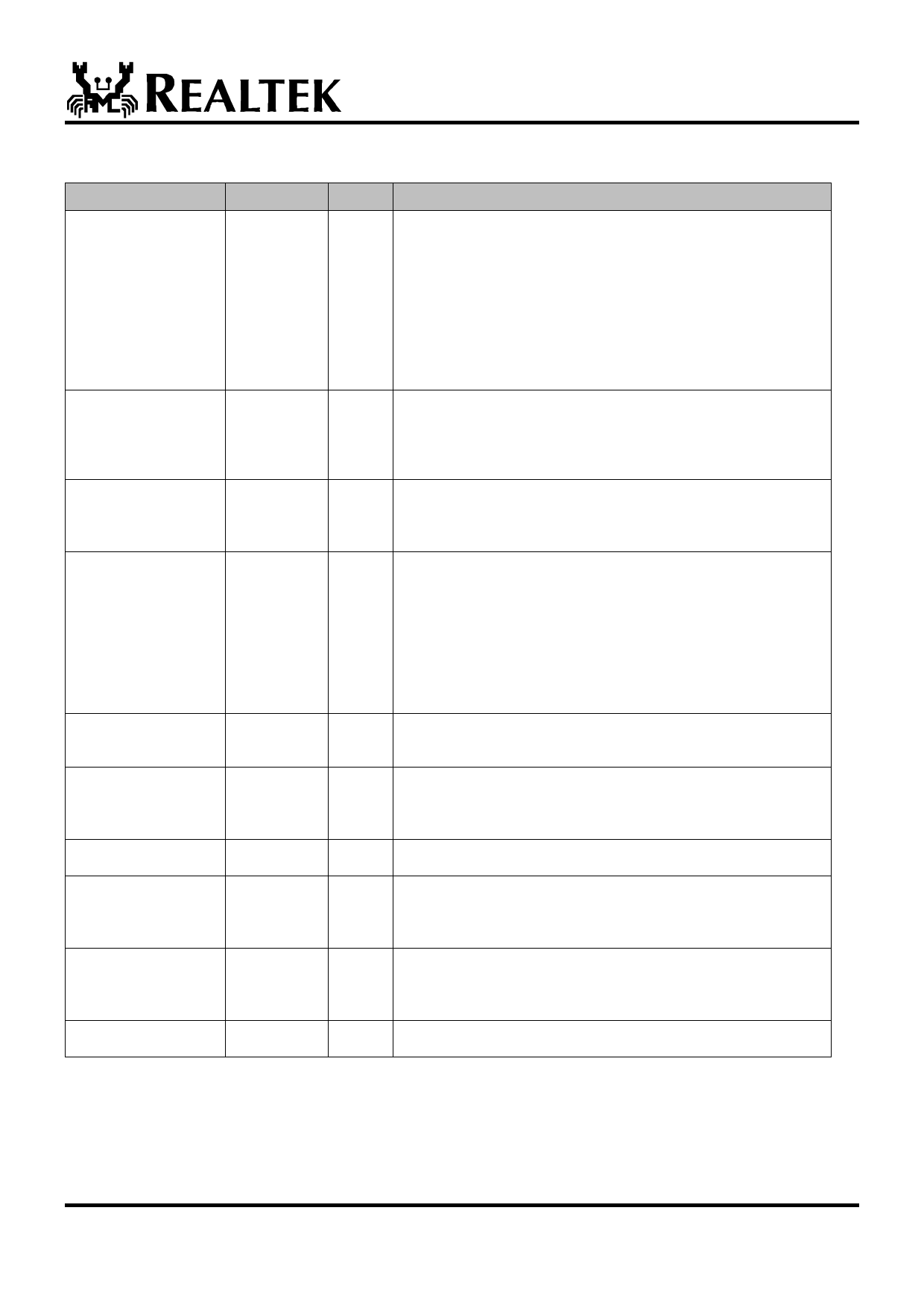

5.4 RMII/SMII/SS-SMII Pins

Pin Name

TXD0[7:0]

TXD1[7:0]

TX_EN [7:0]

RXD0[7:0]

RXD1[7:0]

CRS_DV[7:0]

RX_CLK/

CRS_DV[4]

RX_SYNC

Pin

55,63,69,77,

87,95,101,109

54,62,68,76,

86,94,100,108

56,64,70,78,

88,96,102,110

52,60,66,74,

84,92,98,106

51,59,65,73,

83,91,97,105

53,61,67,75,

85,93,99,107

75

81

Type

I

I

I

O

O

O

O

I/O

Description

Transmit Data Input (bit 0):

In RMII, TXD0 and TXD1 are the di-bits input transmitted and driven

synchronously to REFCLK from MAC.

In SMII, TXD0 inputs the data that is transmitted and is driven

synchronously to REFCLK. In 100Mbps, TXD0 inputs a new 10-bit

segment starting with SYNC. In 10Mbps, TXD0 must repeat each

10-bit segment 10 times.

In SS-SMII, TXD0 behaves as SMII except synchronous to TX_CLK

instead of REFCLK and 10-bit segment starting with TX_SYNC

instead of SYNC.

Transmit Data Input (bit 1):

In RMII, TXD1 and TXD0 are the input di-bits synchronously to

REFCLK.

In SMII/SS-SMII, TXD1 is not used and should be tied either high or

low.

Transmit Enable:

In RMII , TX_EN indicates the di-bits on TXD is valid and is

synchronous to REFCLK.

In SMII/SS-SMII, TX_EN[7:0] are not used.

Receive Data Input (bit 0):

In RMII, RXD0 and RXD1 output di-bits synchronously to REFCLK.

In SMII, RXD0 outputs data or inband management information

synchronously to REFCLK. In 100Mbps, RXD0 outputs a new 10-bit

segment starting with SYNC. In 10Mbps, RXD0 must repeat each

10-bit segment 10 times.

In SS-SMII, RXD0 behaves as SMII except synchronous to RX_CLK

instead of REFCLK and 10-bit segment starting with RX_SYNC

instead of SYNC.

Receive Data Input (bit 1):

In RMII, RXD1 and RXD0 output di-bits synchronously to REFCLK.

In SMII/SS-SMII, RXD1is not used and they are driven low.

Carrier Sense and Data Valid:

In RMII, CRS_DV is asynchronous to REFCLK and asserts when the

medium is non-idle.

In SMII/SS-SMII, CRS_DV[7:0] are not used and driven low.

Receive Clock: In SS-SMII, CRS_DV[4] of RMII is used as

RX_CLK, which is a 125MHz clock output.

Receive Synchronous :

In SS-SMII, RX_SYNC is a sync signal used to delimit the 10-bit

segment of RXD0 for all ports.

SYNC/

TX_SYNC

TX_CLK/

TX_EN[4]

80

I Sync/Transmit Synchronous: In SMII, SYNC is a sync signal used

to delimit a 10-bit segment of RXD0 and TXD0 for all ports.

In SS-SMII, TX_SYNC is a sync signal used to delimit the 10-bit

segment of TXD0 for all ports.

78

I Transmit Clock/Transmit Enable: In SS-SMII, TX_EN[4] of RMII

is used as TX_CLK, which is a 125MHz clock input from MAC.

2003/04/04

8

Rev.1.97