ACS8522 데이터 시트보기 (PDF) - Semtech Corporation

부품명

상세내역

제조사

ACS8522 Datasheet PDF : 118 Pages

| |||

ACS8522 SETS LITE

ADVANCED COMMUNICATIONS

FINAL

DATASHEET

Input Reference Clock Ports

Locking Frequency Modes

Table 4 gives details of the input reference ports, showing

the input technologies and the range of frequencies

supported on each port; the default spot frequencies and

default priorities assigned to each port on power-up or by

reset are also shown. Note that SDH and SONET networks

use different default frequencies; the network type is pin-

selectable (using either the SONSDHB pin or via

software). Specific frequencies and priorities are set by

configuration.

The input ports are fully interchangeable.

SDH and SONET networks use different default

frequencies; the network type is selectable using

cnfg_input_mode Reg. 34, Bit 2 ip_sonsdhb.

z For SONET, ip_sonsdhb = 1

z For SDH, ip_sonsdhb = 0

On power-up or by reset, the default will be set by the state

of the SONSDHB pin (pin 64). Specific frequencies and

priorities are set by configuration.

The frequency selection is programmed via the

cnfg_ref_source_frequency register (Reg. 22, 23, 27 and

28).

There are three locking frequency modes that can be

configured: Direct Lock, Lock 8k and DivN.

Direct Lock Mode

In Direct Lock Mode, the internal DPLL can lock to the

selected input at the spot frequency of the input, for

example 19.44 MHz performs the DPLL phase

comparisons at 19.44 MHz.

In Lock8K and DivN modes an internal divider is used

prior to the DPLL to divide the input frequency before it is

used for phase comparisons in the DPLL.

Lock8K Mode

Lock8K mode automatically sets the divider parameters

to divide the input frequency down to 8 kHz. Lock8K can

only be used on the supported spot frequencies (see

Table 4 Note(i)). Lock8k mode is enabled by setting the

Lock8k bit (Bit 6) in the appropriate

cnfg_ref_source_frequency register location. Using lower

frequencies for phase comparisons in the DPLL results in

a greater tolerance to input jitter. It is possible to choose

which edge of the input reference clock to lock to, by

setting 8K edge polarity (Bit 2 of Reg. 03, test_register1).

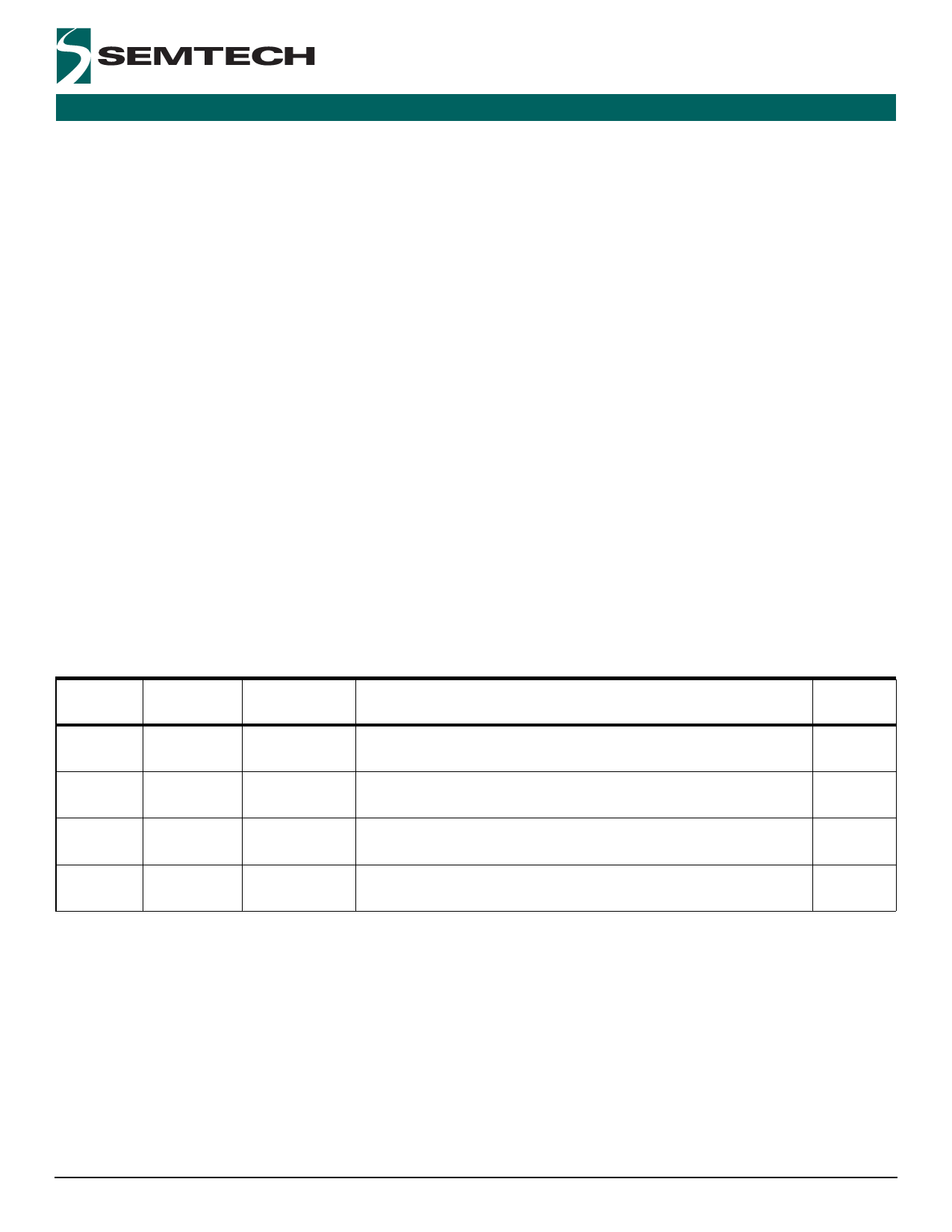

Table 4 Input Reference Source Selection and Priority Table

Input Port

Channel

Number (Bin)

Input Port

Technology

SEC1

0011

TTL/CMOS

SEC2

0100

TTL/CMOS

SEC3

1000

TTL/CMOS

SEC4

1001

TTL/CMOS

Frequencies Supported

Up to 100 MHz (see Note (i))

Default (SONET): 8 kHz Default (SDH): 8 kHz

Up to 100 MHz (see Note (i))

Default (SONET): 8 kHz Default (SDH): 8 kHz

Up to 100 MHz (see Note (i))

Default (SONET): 19.44 MHz Default (SDH): 19.44 MHz

Up to 100 MHz (see Note (i))

Default (SONET): 19.44 MHz Default (SDH): 19.44 MHz

Default

Priority

2

3

4

5

Note: (i) TTL ports (compatible also with CMOS signals) support clock speeds up to 100 MHz, with the highest spot frequency being

77.76 MHz. The actual spot frequencies are: 2 kHz, 4 kHz, 8 kHz (and N x 8 kHz), 1.544 MHz (SONET)/2.048 MHz (SDH), 6.48 MHz,

19.44 MHz, 25.92 MHz, 38.88 MHz, 51.84 MHz, 77.76 MHz. SONET or SDH input rate is selected via Reg. 34 Bit 2, ip_sonsdhb).

Revision 5/November 2006 © Semtech Corp.

Page 9

www.semtech.com