AD6653 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

제조사

AD6653 Datasheet PDF : 80 Pages

| |||

AD6653

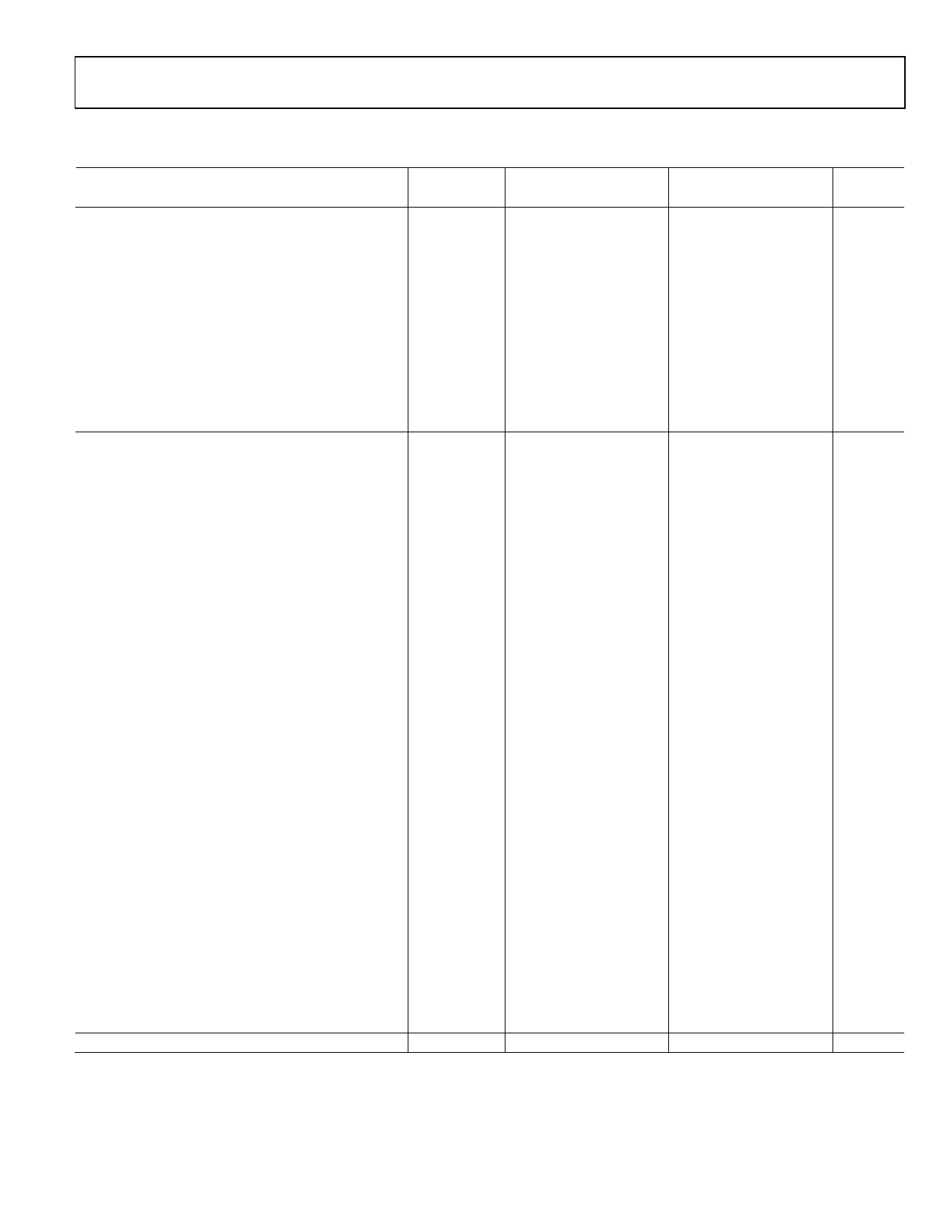

SWITCHING SPECIFICATIONS

Table 4.

Parameter

CLOCK INPUT PARAMETERS

Input Clock Rate

Conversion Rate1

DCS Enabled

DCS Disabled

CLK Period—Divide-by-1 Mode (tCLK)

CLK Pulse Width High (tCLKH)

Divide-by-1 Mode, DCS Enabled

Divide-by-1 Mode, DCS Disabled

Divide-by-2 Mode, DCS Enabled

Divide-by-3 Through Divide-by-8 Modes,

DCS Enabled

DATA OUTPUT PARAMETERS (DATA, FD)

CMOS Noninterleaved Mode—DRVDD = 1.8 V

Data Propagation Delay (tPD)2

DCO Propagation Delay (tDCO)

Setup Time (tS)

Hold Time (tH)

CMOS Noninterleaved Mode—DRVDD = 3.3 V

Data Propagation Delay (tPD)2

DCO Propagation Delay (tDCO)

Setup Time (tS)

Hold Time (tH)

CMOS Interleaved and IQ Mode—DRVDD = 1.8 V

Data Propagation Delay (tPD)2

DCO Propagation Delay (tDCO)

Setup Time (tS)

Hold Time (tH)

CMOS Interleaved and IQ Mode—DRVDD = 3.3 V

Data Propagation Delay (tPD) 2

DCO Propagation Delay (tDCO)

Setup Time (tS)

Hold Time (tH)

LVDS Mode—DRVDD = 1.8 V

Data Propagation Delay (tPD)2

DCO Propagation Delay (tDCO)

Pipeline Delay (Latency) NCO, FIR, fS/8 Mix Disabled

Pipeline Delay (Latency) NCO Enabled; FIR and fS/8

Mix Disabled (Complex Output Mode)

Pipeline Delay (Latency) NCO, FIR Filter, and fS/8 Mix

Enabled

Aperture Delay (tA)

Aperture Uncertainty (Jitter, tJ)

Wake-Up Time3

OUT-OF-RANGE RECOVERY TIME

Temperature

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

AD6653BCPZ-125

Min Typ Max

625

20

125

10

125

8

2.4 4

5.6

3.6 4

4.4

1.6

0.8

1.6 3.9 6.2

4.0 5.4 7.3

9.5

6.5

1.9 4.1 6.4

4.4 5.8 7.7

9.7

6.3

1.6 3.9 6.2

3.4 4.8 6.7

4.9

3.1

1.9 4.1 6.4

3.8 5.2 7.1

5.1

2.9

2.5 4.8 7.0

3.7 5.3 7.3

38

38

109

1.0

0.1

350

44

1 Conversion rate is the clock rate after the divider.

2 Output propagation delay is measured from CLK 50% transition to DATA 50% transition, with a 5 pF load.

3 Wake-up time is dependent on the value of the decoupling capacitors.

AD6653BCPZ-150

Min Typ Max

625

20

150

10

150

6.66

2.0 3.33 4.66

3.0 3.33 3.66

1.6

0.8

1.6 3.9 6.2

4.0 5.4 7.3

8.16

5.16

1.9 4.1 6.4

4.4 5.8 7.7

8.36

4.96

1.6 3.9 6.2

3.4 4.8 6.7

4.23

2.43

1.9 4.1 6.4

3.8 5.2 7.1

4.43

2.23

2.5 4.8 7.0

3.7 5.3 7.3

38

38

109

1.0

0.1

350

44

Unit

MHz

MSPS

MSPS

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Cycles

Cycles

Cycles

ns

ps rms

μs

Cycles

Rev. 0 | Page 9 of 80