RTL8139C 데이터 시트보기 (PDF) - Realtek Semiconductor

부품명

상세내역

제조사

RTL8139C

RTL8139C Datasheet PDF : 62 Pages

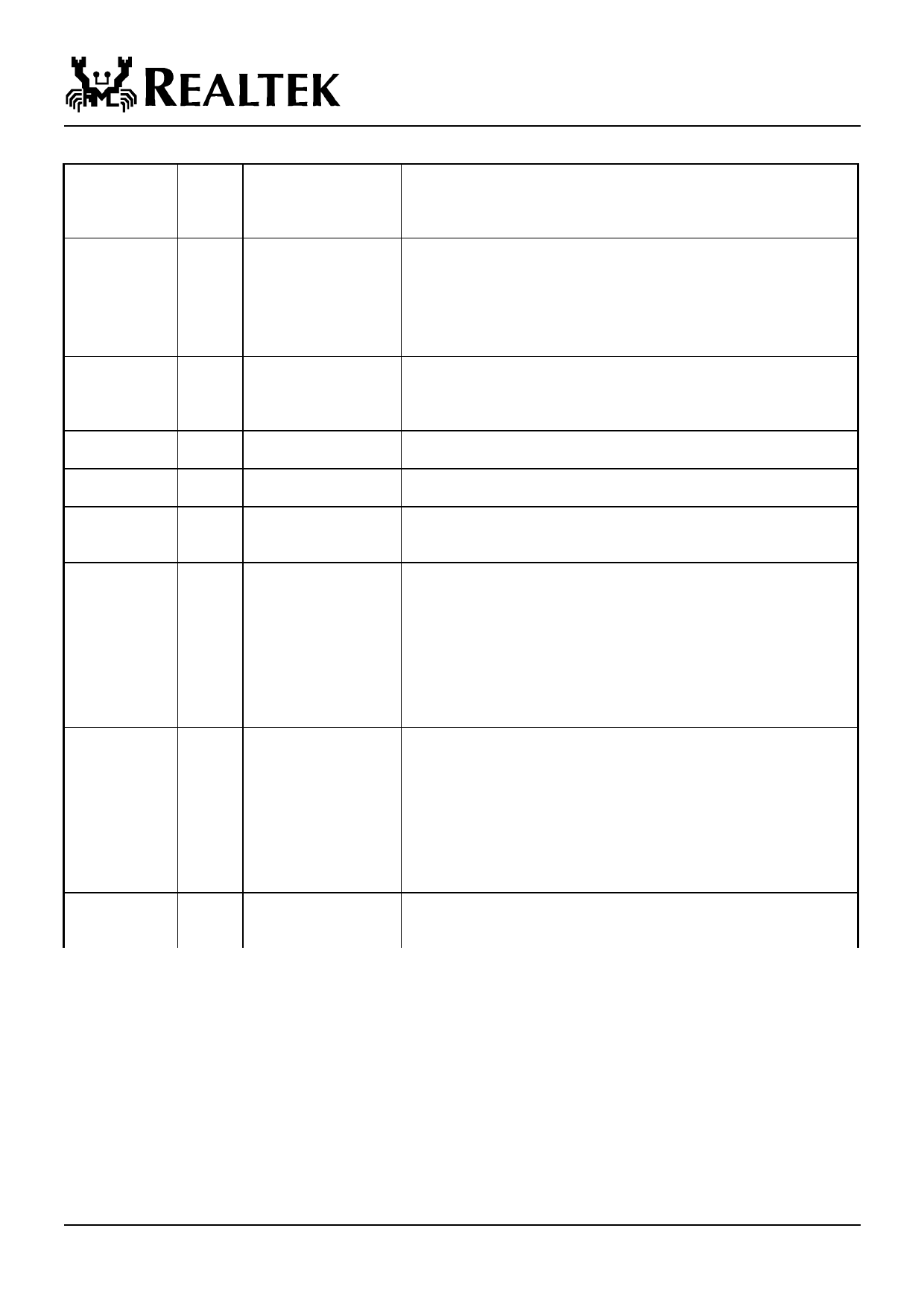

| |||

DEVSELB

S/T/S

FRAMEB

S/T/S

GNTB

REQB

IDSEL

INTAB

IRDYB

I

T/S

I

O/D

S/T/S

TRDYB

S/T/S

PAR

T/S

RTL8139C(L)

19

Device Select: As a bus master, the RTL8139C(L) samples this signal

to insure that a PCI target recognizes the destination address for the data

transfer. As a target, the RTL8139C(L) asserts this signal low when it

recognizes its target address after FRAMEB is asserted.

15

Cycle Frame: As a bus master, this pin indicates the beginning and

duration of an access. FRAMEB is asserted low to indicate the start of a

bus transaction. While FRAMEB is asserted, data transfer continues.

When FRAMEB is deasserted, the transaction is in the final data phase.

As a target, the device monitors this signal before decoding the address

to check if the current transaction is addressed to it.

117

Grant: This signal is asserted low to indicate to the RTL8139C(L) that

the central arbiter has granted ownership of the bus to the

RTL8139C(L). This input is used when the RTL8139C(L) is acting as a

bus master.

118

Request: The RTL8139C(L) will assert this signal low to request the

ownership of the bus from the central arbiter.

3

Initialization Device Select: This pin allows the RTL8139C(L) to

identify when configuration read/write transactions are intended for it.

114

Interrupt A: Used to request an interrupt. It is asserted low when an

interrupt condition occurs, as defined by the Interrupt Status, Interrupt

Mask and Interrupt Enable registers.

16

Initiator Ready: This indicates the initiating agent’s ability to complete

the current data phase of the transaction.

As a bus master, this signal will be asserted low when the

RTL8139C(L) is ready to complete the current data phase transaction.

This signal is used in conjunction with the TRDYB signal. Data

transaction takes place at the rising edge of CLK when both IRDYB and

TRDYB are asserted low. As a target, this signal indicates that the

master has put data on the bus.

17

Target Ready: This indicates the target agent’s ability to complete the

current phase of the transaction.

As a bus master, this signal indicates that the target is ready for the data

during write operations and with the data during read operations. As a

target, this signal will be asserted low when the (slave) device is ready

to complete the current data phase transaction. This signal is used in

conjunction with the IRDYB signal. Data transaction takes place at the

rising edge of CLK when both IRDYB and TRDYB are asserted low.

23

Parity: This signal indicates even parity across AD31-0 and C/BE3-0

including the PAR pin. As a master, PAR is asserted during address and

write data phases. As a target, PAR is asserted during read data phases.

2002/01/10

7

Rev.1.4