ADG2128BCPZ-REEL(RevA) 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

제조사

ADG2128BCPZ-REEL

(Rev.:RevA)

(Rev.:RevA)

ADG2128BCPZ-REEL Datasheet PDF : 28 Pages

| |||

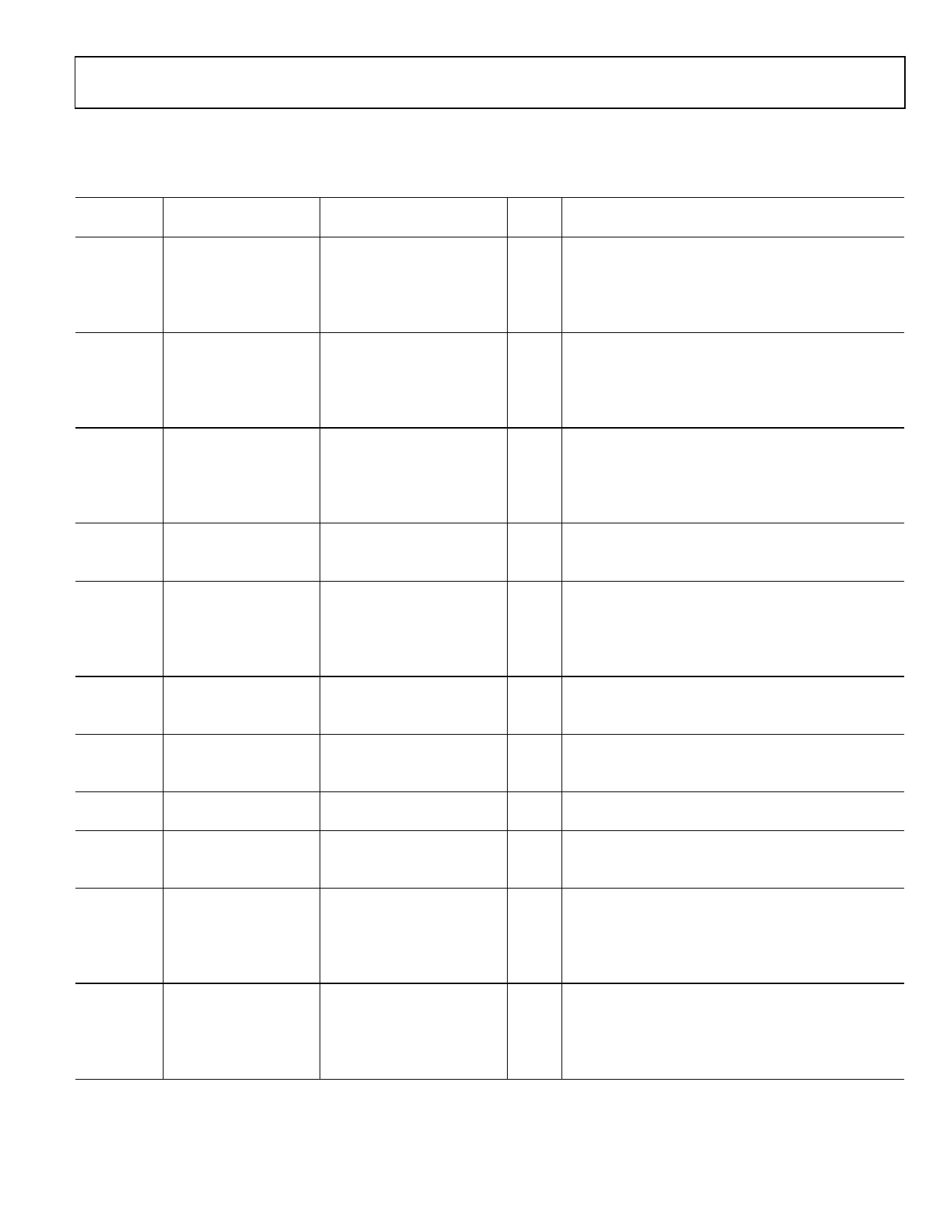

ADG2128

I2C TIMING SPECIFICATIONS

VDD = 5 V to 12 V; VSS = −5 V to 0 V; VL = 5 V; GND = 0 V; TA = TMIN to TMAX, unless otherwise noted (see Figure 2).

Table 3.

Parameter1 Conditions

ADG2108 Limit at TMIN, TMAX

Min

Max

Unit

fSCL

Standard mode

100

kHz

Fast mode

400

kHz

High speed mode2

CB = 100 pF maximum

3.4

MHz

CB = 400 pF maximum

1.7

MHz

t1

Standard mode

4

μs

Fast mode

0.6

μs

High speed mode2

CB = 100 pF maximum 60

ns

CB = 400 pF maximum 120

ns

t2

Standard mode

4.7

μs

Fast mode

1.3

μs

High speed mode2

CB = 100 pF maximum 160

ns

CB = 400 pF maximum 320

ns

t3

Standard mode

250

ns

Fast mode

100

ns

High speed mode2

10

ns

t4 3

Standard mode

0

3.45

μs

Fast mode

0

0.9

μs

High speed mode2

CB = 100 pF maximum 0

70

ns

CB = 400 pF maximum 0

150

ns

t5

Standard mode

4.7

μs

Fast mode

0.6

μs

High speed mode2

160

ns

t6

Standard mode

4

μs

Fast mode

0.6

μs

High speed mode2

160

ns

t7

Standard mode

4.7

μs

Fast mode

1.3

μs

t8

Standard mode

4

μs

Fast mode

0.6

μs

High speed mode2

160

ns

t9

Standard mode

1000

ns

Fast mode

20 + 0.1 CBB

300

ns

High speed mode2

CB = 100 pF maximum 10

80

ns

CB = 400 pF maximum 20

160

ns

t10

Standard mode

300

ns

Fast mode

20 + 0.1 CBB

300

ns

High speed mode2

CB = 100 pF maximum 10

80

ns

CB = 400 pF maximum 20

160

ns

Description

Serial clock frequency

tHIGH, SCL high time

tLOW, SCL low time

tSU;DAT, data setup time

tHD;DAT, data hold time

tSU;STA, setup time for a repeated start condition

tHD;STA, hold time for a repeated start condition

tBUF, bus free time between a stop and a start condition

tSU;STO, setup time for a stop condition

tRDA, rise time of SDA signal

tFDA, fall time of SDA signal

Rev. A | Page 7 of 28