ADSP-BF537BBCZ-5AV 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

제조사

ADSP-BF537BBCZ-5AV Datasheet PDF : 68 Pages

| |||

ADSP-BF534/ADSP-BF536/ADSP-BF537

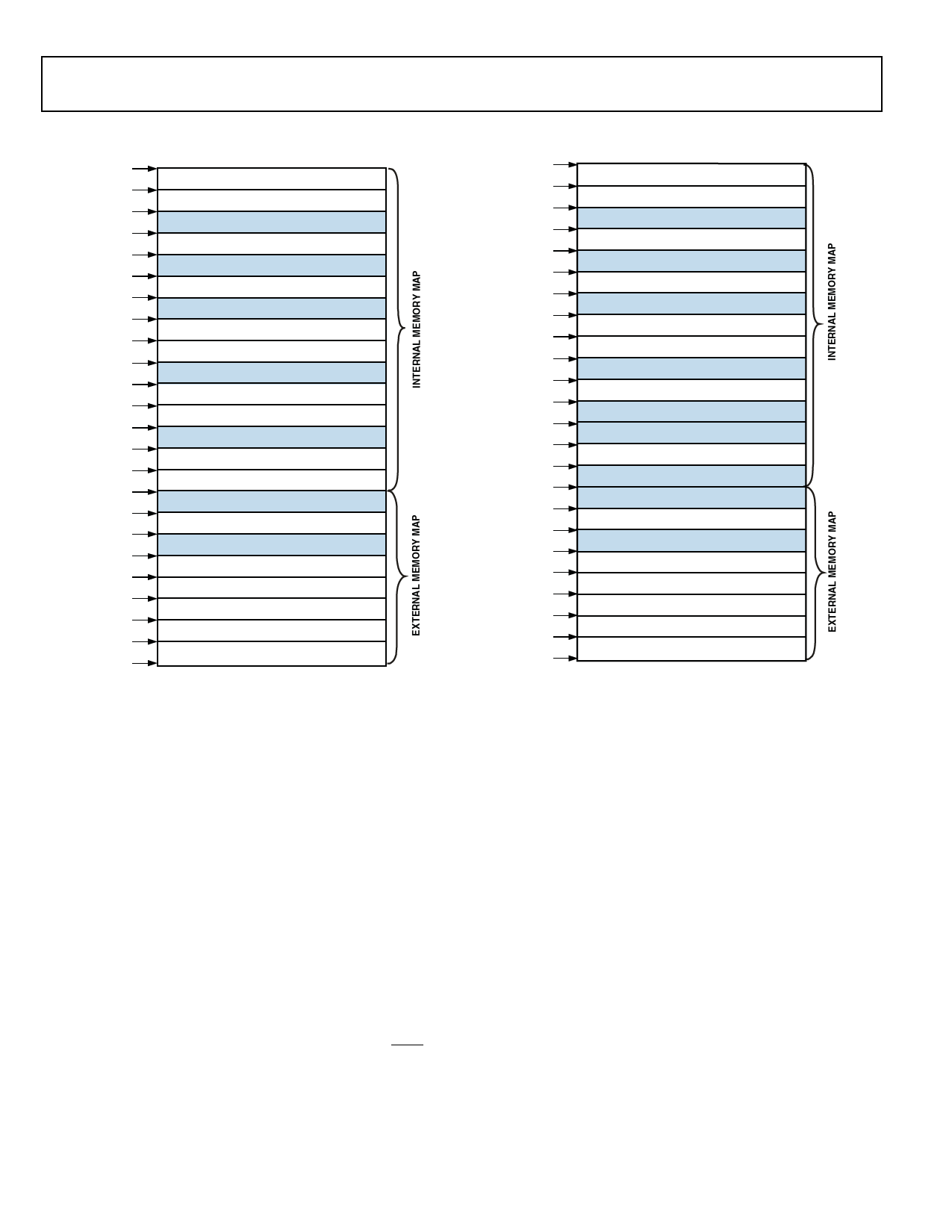

ADSP-BF534/ADSP-BF537 MEMORY MAP

0xFFFF FFFF

0xFFE0 0000

0xFFC0 0000

0xFFB0 1000

0xFFB0 0000

0xFFA1 4000

0xFFA1 0000

0xFFA0 C000

0xFFA0 8000

0xFFA0 0000

0xFF90 8000

0xFF90 4000

0xFF90 0000

0xFF80 8000

0xFF80 4000

0xFF80 0000

0xEF00 0800

0xEF00 0000

0x2040 0000

0x2030 0000

0x2020 0000

0x2010 0000

0x2000 0000

0x0000 0000

CORE MMR REGISTERS (2M BYTES)

SYSTEM MMR REGISTERS (2M BYTES)

RESERVED

SCRATCHPAD SRAM (4K BYTES)

RESERVED

INSTRUCTION SRAM/CACHE (16K BYTES)

RESERVED

INSTRUCTION BANK B SRAM (16K BYTES)

INSTRUCTION BANK A SRAM (32K BYTES)

RESERVED

DATA BANK B SRAM/CACHE (16K BYTES)

DATA BANK B SRAM (16K BYTES)

RESERVED

DATA BANK A SRAM/CACHE (16K BYTES)

DATA BANK A SRAM (16K BYTES)

RESERVED

BOOT ROM (2K BYTES)

RESERVED

ASYNC MEMORY BANK 3 (1M BYTES)

ASYNC MEMORY BANK 2 (1M BYTES)

ASYNC MEMORY BANK 1 (1M BYTES)

ASYNC MEMORY BANK 0 (1M BYTES)

SDRAM MEMORY (16M BYTES TO 512M BYTES)

0xFFFF FFFF

0xFFE0 0000

0xFFC0 0000

0xFFB0 1000

0xFFB0 0000

0xFFA1 4000

0xFFA1 0000

0xFFA0 C000

0xFFA0 8000

0xFFA0 0000

0xFF90 8000

0xFF90 4000

0xFF90 0000

0xFF80 8000

0xFF80 4000

0xFF80 0000

0xEF00 0800

0xEF00 0000

0x2040 0000

0x2030 0000

0x2020 0000

0x2010 0000

0x2000 0000

0x0000 0000

ADSP-BF536 MEMORY MAP

CORE MMR REGISTERS (2M BYTES)

SYSTEM MMR REGISTERS (2M BYTES)

RESERVED

SCRATCHPAD SRAM (4K BYTES)

RESERVED

INSTRUCTION SRAM/CACHE (16K BYTES)

RESERVED

INSTRUCTION BANK B SRAM (16K BYTES)

INSTRUCTION BANK A SRAM (32K BYTES)

RESERVED

DATA BANK B SRAM/CACHE (16K BYTES)

RESERVED

RESERVED

DATA BANK A SRAM/CACHE (16K BYTES)

RESERVED

RESERVED

BOOT ROM (2K BYTES)

RESERVED

ASYNC MEMORY BANK 3 (1M BYTES)

ASYNC MEMORY BANK 2 (1M BYTES)

ASYNC MEMORY BANK 1 (1M BYTES)

ASYNC MEMORY BANK 0 (1M BYTES)

SDRAM MEMORY (16M BYTES TO 512M BYTES)

Figure 3. ADSP-BF534/ADSP-BF536/ADSP-BF537 Memory Maps

memory space, the processor starts executing from the on-chip

boot ROM. For more information, see Booting Modes on

Page 16.

Event Handling

The event controller on the Blackfin processor handles all asyn-

chronous and synchronous events to the processor. The

Blackfin processor provides event handling that supports both

nesting and prioritization. Nesting allows multiple event service

routines to be active simultaneously. Prioritization ensures that

servicing of a higher priority event takes precedence over servic-

ing of a lower priority event. The controller provides support for

five different types of events:

• Emulation – An emulation event causes the processor to

enter emulation mode, allowing command and control of

the processor via the JTAG interface.

• Reset – This event resets the processor.

• Nonmaskable Interrupt (NMI) – The NMI event can be

generated by the software watchdog timer or by the NMI

input signal to the processor. The NMI event is frequently

used as a power-down indicator to initiate an orderly shut-

down of the system.

• Exceptions – Events that occur synchronously to program

flow (in other words, the exception is taken before the

instruction is allowed to complete). Conditions such as

data alignment violations and undefined instructions cause

exceptions.

• Interrupts – Events that occur asynchronously to program

flow. They are caused by input pins, timers, and other

peripherals, as well as by an explicit software instruction.

Each event type has an associated register to hold the return

address and an associated return-from-event instruction. When

an event is triggered, the state of the processor is saved on the

supervisor stack.

The Blackfin processor event controller consists of two stages:

the core event controller (CEC) and the system interrupt con-

troller (SIC). The core event controller works with the system

interrupt controller to prioritize and control all system events.

Conceptually, interrupts from the peripherals enter into the

SIC, and are then routed directly into the general-purpose inter-

rupts of the CEC.

Rev. J | Page 6 of 68 | February 2014