IS42G32256-8PQ 데이터 시트보기 (PDF) - Integrated Silicon Solution

부품명

상세내역

제조사

IS42G32256-8PQ Datasheet PDF : 52 Pages

| |||

IS42G32256

ISSI ®

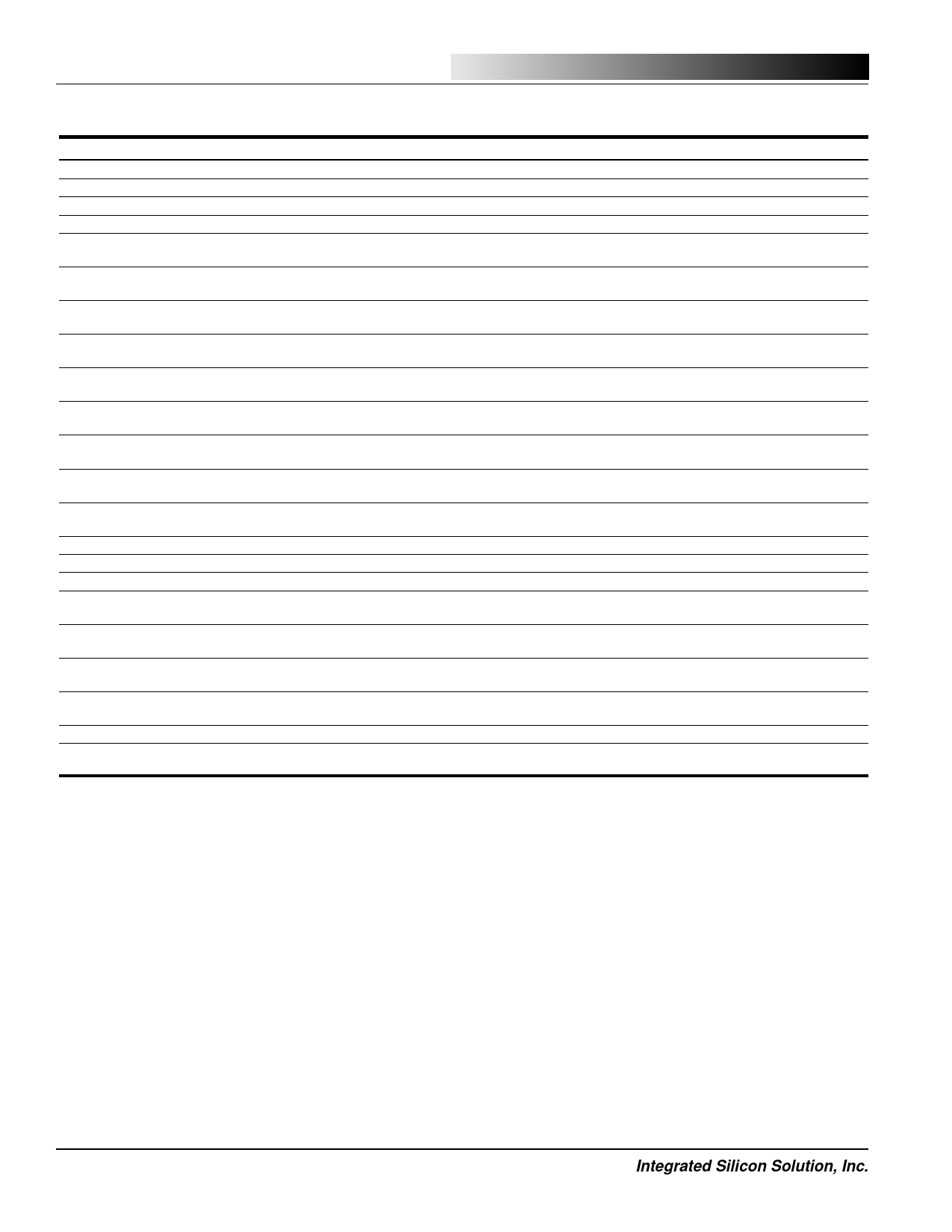

Table 4. Truth Table

Function

CKEn-1 CKEn

CS RAS CAS WE DSF DQM A10 A9 A8-A0

Mode Register Set(2,3)

H

X

L

L

L

L

L

X

OP CODE

Special Mode Register Set(2,3,8)

H

X

L

L

L

L

H

X

OP CODE

Auto Refresh(4)

H

H

L

L

L

H

L

X

XXX

Self Refresh, Entry(4)

H

L

L

L

L

H

L

X

XXX

Self Refresh, Exit(4)

L

H

L

H

H

H

X

X

XXX

L

H

H

X

X

X

X

X

XXX

Bank Active/Row Address

Write Per Bit Disable(5,6)

H

X

L

L

H

H

L

X

V

Row

Address

Bank Active/Row Address

Write Per Bit Enable(5,6,10)

H

X

L

L

H

H

H

X

V

Row

Address

Read and Column Address

Auto Precharge Disable(5)

H

X

L

H

L

H

L

X

V L Column

Address

Read and Column Address

Auto Precharge Enable(5,6)

H

X

L

H

L

H

L

X

V H Column

Address

Write and Column Address

Auto Precharge Disable(5,6)

H

X

L

H

L

L

L

X

V L Column

Address

Write and Column Address

Auto Precharge Enable(5,6,7,10)

H

X

L

H

L

L

L

X

V H Column

Address

Block Write and Column Address

Auto Precharge Disable(5,6)

H

X

L

H

L

L

H

X

V L Column

Address

Block Write and Column Address

Auto Precharge Enable(5,6,7,10)

H

X

L

H

L

L

H

X

V H Column

Address

Burst Stop(8)

H

X

L

H

H

L

L

X

XXX

Precharge Bank Selection

H

X

L

L

H

L

L

X

VLX

Precharge Both Banks

H

X

L

L

H

L

L

X

XHX

Clock Suspend or

Active Power Down Entry

H

L

L

H

H

H

X

X

XXX

H

L

H

X

X

X

X

X

XXX

Clock Suspend or

Active Power Down Exit

L

H

X

X

X

X

X

X

XXX

Precharge Pover Down Mode Entry

H

L

L

H

H

H

X

X

XXX

H

L

H

X

X

X

X

X

XXX

Precharge Pover Down Mode Exit

L

H

L

V

V

V

V

X

XXX

L

H

H

X

X

X

X

X

XXX

DQM(9)

H

X

X

X

X

X

X

V

XXX

No Operation Command

H

X

L

H

H

H

X

X

XXX

H

X

H

X

X

X

X

X

XXX

Notes:

1. V = Valid, X = Don’t Care, H = Logic High, L = Logic Low

2. OP Code: Operand Code; A0-A10: Program keys (@MRS); A5, A6: LMR or LCR select. (@SMRS) Color register exists only

one per DQi which both banks share. So does Mask Register. Color or mask is loaded into chip through DQ pin.

3. MRS can be issued only at both banks precharge state. SMRS can be issued only if DQs are idle. A new command can be

issued at the next clock of MRS/SMRS.

4. Auto refresh functions as same as CBR refresh of DRAM. The automatical precharge without row precharge command is

meant by “Auto”. Auto/Self refresh can be issued only at both precharge state.

5. A10: bank select address. If “Low” at read, (block) write, row active and precharge, bank A is selected. If “High” at read,

(block) write, row active and precharge, bank B is selected. If A9 is “High” at row precharge, A10 is ignored and both banks

are precharged.

6. It is determined at row active cycle whether normal/block write operates in write per bit mode or not. For A bank write, at A

bank row active, for B bank write, at B bank row active. Terminology: Write per bit = I/O mask. (Block) Write with write per bit

mode = masked (block) write.

7. During burst read or write with auto precharge, new read/(block) write command cannot be issued. Another bank read/(block)

write command can be issued at tRP after the end of burst.

8. Burst stop command is valid only at full page burst length.

9. DQM sampled at positive going edge of a CLK masks the data-in at the very CLK (write DQM latency is 0) but makes Hi-Z

state the data-out of 2 CLK cycles after. (Read DQM latency is 2.)

10. Graphic features added to SDRAMs original features. If SDF is tied to low, graphic functions are disabled and chip operates

as a 16M SDRAM with 32 DQs.

6

Integrated Silicon Solution, Inc.

ADVANCE INFORMATION SR037-0C

09/10/98