24AA32-/SN 데이터 시트보기 (PDF) - Microchip Technology

부품명

상세내역

제조사

24AA32-/SN Datasheet PDF : 12 Pages

| |||

24AA32

4.0 WRITE OPERATION

4.1 Split Endurance

The 24AA32 is organized as a continuous 32K block of

memory. However, the first 4K, starting at address 000,

is rated at 10,000,000 E/W cycles guaranteed. The

remainder of the array, 28K bits, is rated at 100,000 E/

W cycles guaranteed. This feature is helpful in applica-

tions in which some data change frequently, while a

majority of the data change infrequently. One example

would be a cellular telephone in which last-number

redial and microcontroller scratch pad require a high-

endurance block, while speed dials and lookup tables

change infrequently and so require only a standard

endurance rating.

4.2 Byte Write

Following the start condition from the master, the con-

trol code (four bits), the device select (three bits), and

the R/W bit which is a logic low are clocked onto the bus

by the master transmitter. This indicates to the

addressed slave receiver that a byte with a word

address will follow after it has generated an acknowl-

edge bit during the ninth clock cycle. Therefore the next

byte transmitted by the master is the high-order byte of

the word address and will be written into the address

pointer of the 24AA32. The next byte is the least signif-

icant address byte. After receiving another acknowl-

edge signal from the 24AA32 the master device will

transmit the data word to be written into the addressed

memory location.

The 24AA32 acknowledges again and the master gen-

erates a stop condition. This initiates the internal write

cycle, and during this time the 24AA32 will not generate

acknowledge signals (Figure 4-1).

4.3 Page Write

The write control byte, word address and the first data

byte are transmitted to the 24AA32 in the same way as

in a byte write. But instead of generating a stop condi-

tion, the master transmits up to eight pages of eight

data bytes each (64 bytes total) which are temporarily

stored in the on-chip page cache of the 24AA32. They

will be written from cache into the EEPROM array after

the master has transmitted a stop condition. After the

receipt of each word, the six lower order address

pointer bits are internally incremented by one. The

higher order seven bits of the word address remain con-

stant. If the master should transmit more than eight

bytes prior to generating the stop condition (writing

across a page boundary), the address counter (lower

three bits) will roll over and the pointer will be incre-

mented to point to the next line in the cache. This can

continue to occur up to eight times or until the cache is

full, at which time a stop condition should be generated

by the master. If a stop condition is not received, the

cache pointer will roll over to the first line (byte 0) of the

cache, and any further data received will overwrite pre-

viously captured data. The stop condition can be sent

at any time during the transfer. As with the byte write

operation, once a stop condition is received, an internal

write cycle will begin. The 64-byte cache will continue

to capture data until a stop condition occurs or the oper-

ation is aborted (Figure 4-2).

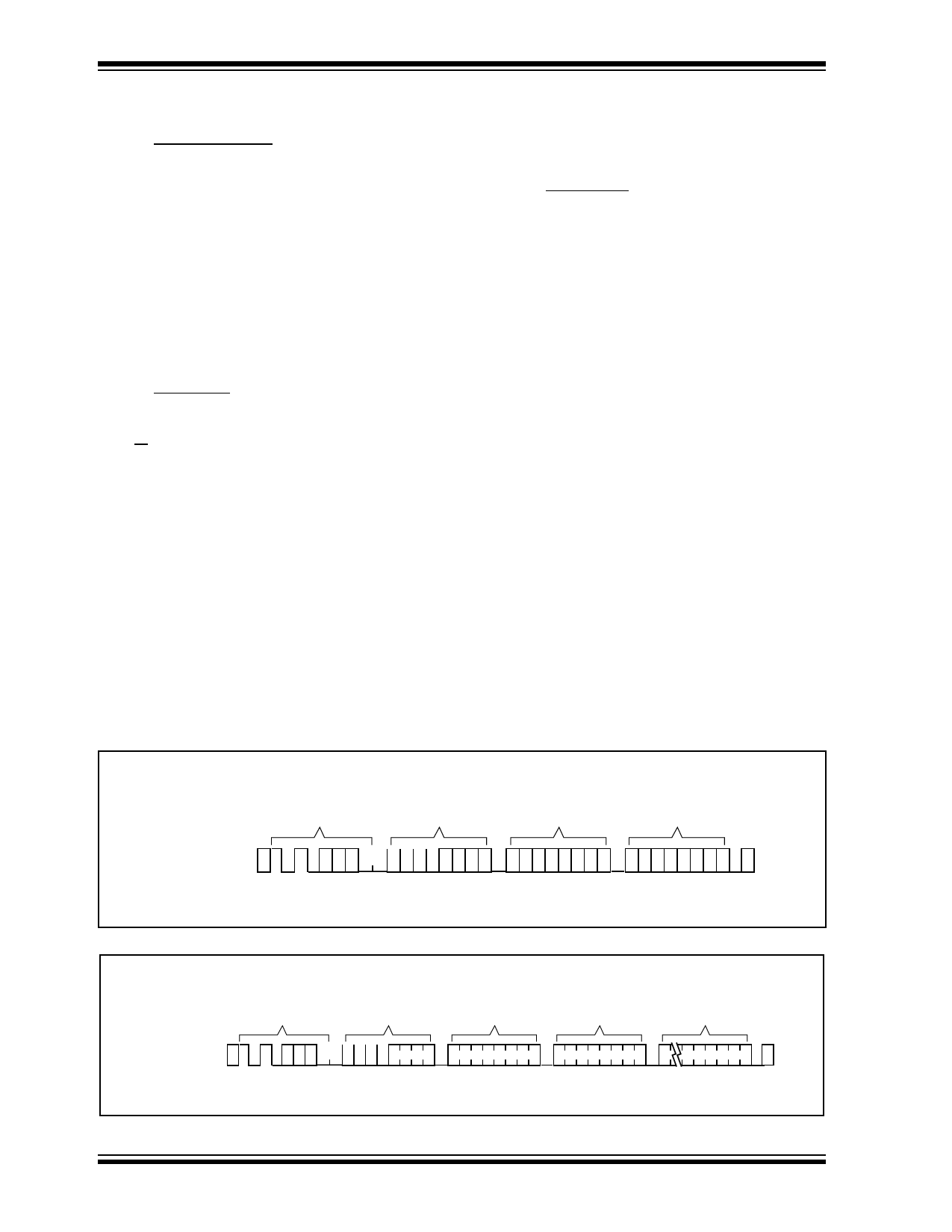

FIGURE 4-1: BYTE WRITE

S

t

Bus Activity:

Master

a

r

t

Control

Byte

Word

Address (1)

Word

Address (0)

S

t

Data

o

p

SDA Line

Bus Activity

0000

A

A

A

C

C

C

K

K

K

FIGURE 4-2: PAGE WRITE (FOR CACHE WRITE, SEE FIGURE 7-1)

S

t

a

Bus Activity: r

Master

t

Control

Byte

Word

Address (1)

Word

Address (0)

Data n

SDA Line

Bus Activity

0000

A

A

A

C

C

C

K

K

K

A

C

K

S

t

Data n + 175

o

p

A

A

C

C

K

K

DS21124C-page 6

© 1996 Microchip Technology Inc.