IS62C256 데이터 시트보기 (PDF) - Integrated Silicon Solution

부품명

상세내역

제조사

IS62C256 Datasheet PDF : 8 Pages

| |||

IS62C256

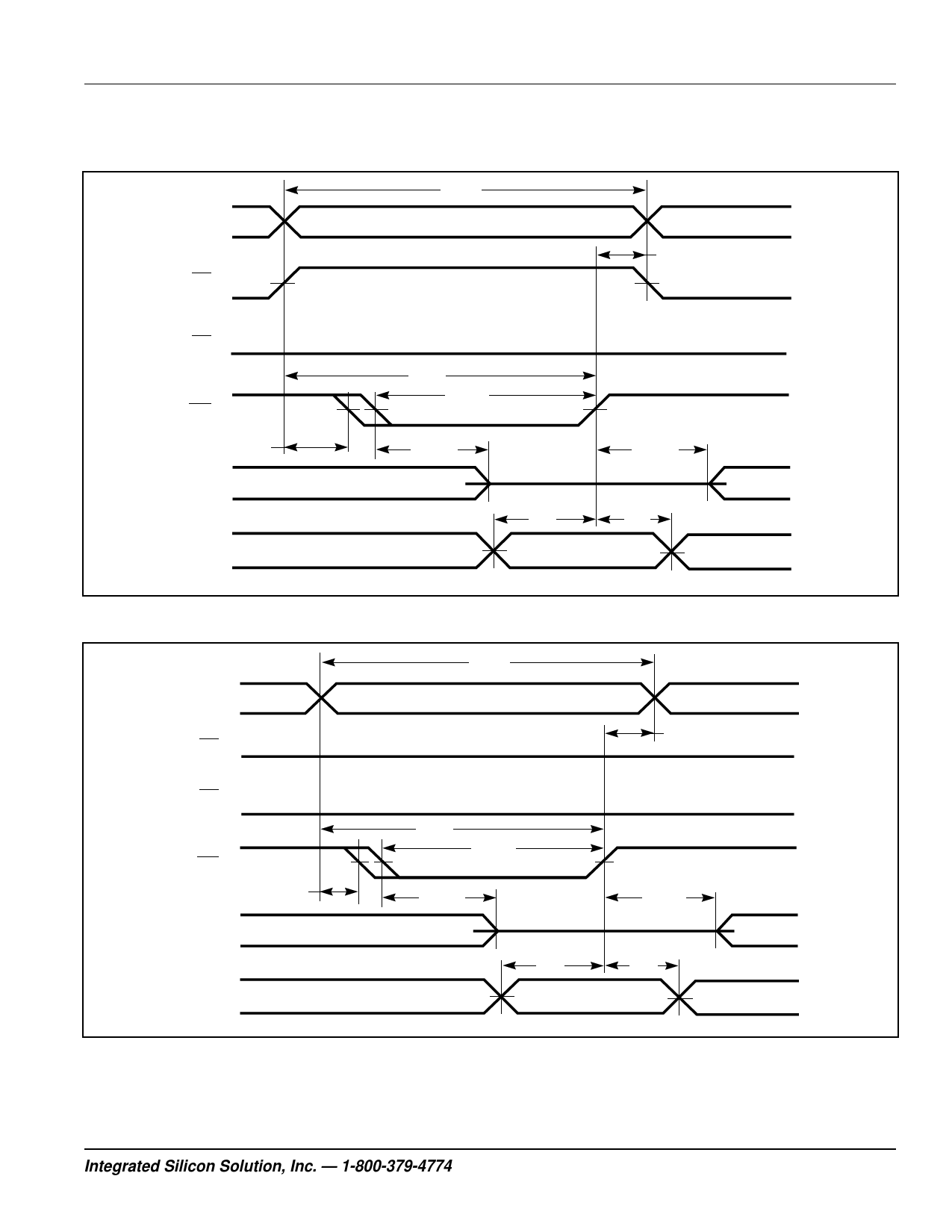

AC WAVEFORMS

WRITE CYCLE NO. 2 (OE is HIGH During Write Cycle) (1,2)

ADDRESS

t WC

VALID ADDRESS

OE

ISSI ®

t HA

CS LOW

WE

DOUT

t SA

DATA UNDEFINED

t AW

t PWE1

t HZWE

DIN

HIGH-Z

t LZWE

t SD

t HD

DATAIN VALID

WRITE CYCLE NO. 3 (OE is LOW During Write Cycle) (1)

t WC

ADDRESS

VALID ADDRESS

t HA

OE LOW

CS_WR2.eps

CS LOW

WE

DOUT

t SA

DATA UNDEFINED

t AW

t PWE2

t HZWE

HIGH-Z

t LZWE

t SD

t HD

DIN

DATAIN VALID

CS_WR3.eps

Notes:

1. The internal write time is defined by the overlap of Cs LOW and WE LOW. All signals must be in valid states to initiate a Write,

but any one can go inactive to terminate the Write. The Data Input Setup and Hold timing are referenced to the rising or falling

edge of the signal that terminates the write.

2. I/O will assume the High-Z state if OE = VIH.

Integrated Silicon Solution, Inc. — 1-800-379-4774

7

SR072-1E

05/12/99