CY3683(2008) 데이터 시트보기 (PDF) - Cypress Semiconductor

부품명

상세내역

제조사

CY3683 Datasheet PDF : 15 Pages

| |||

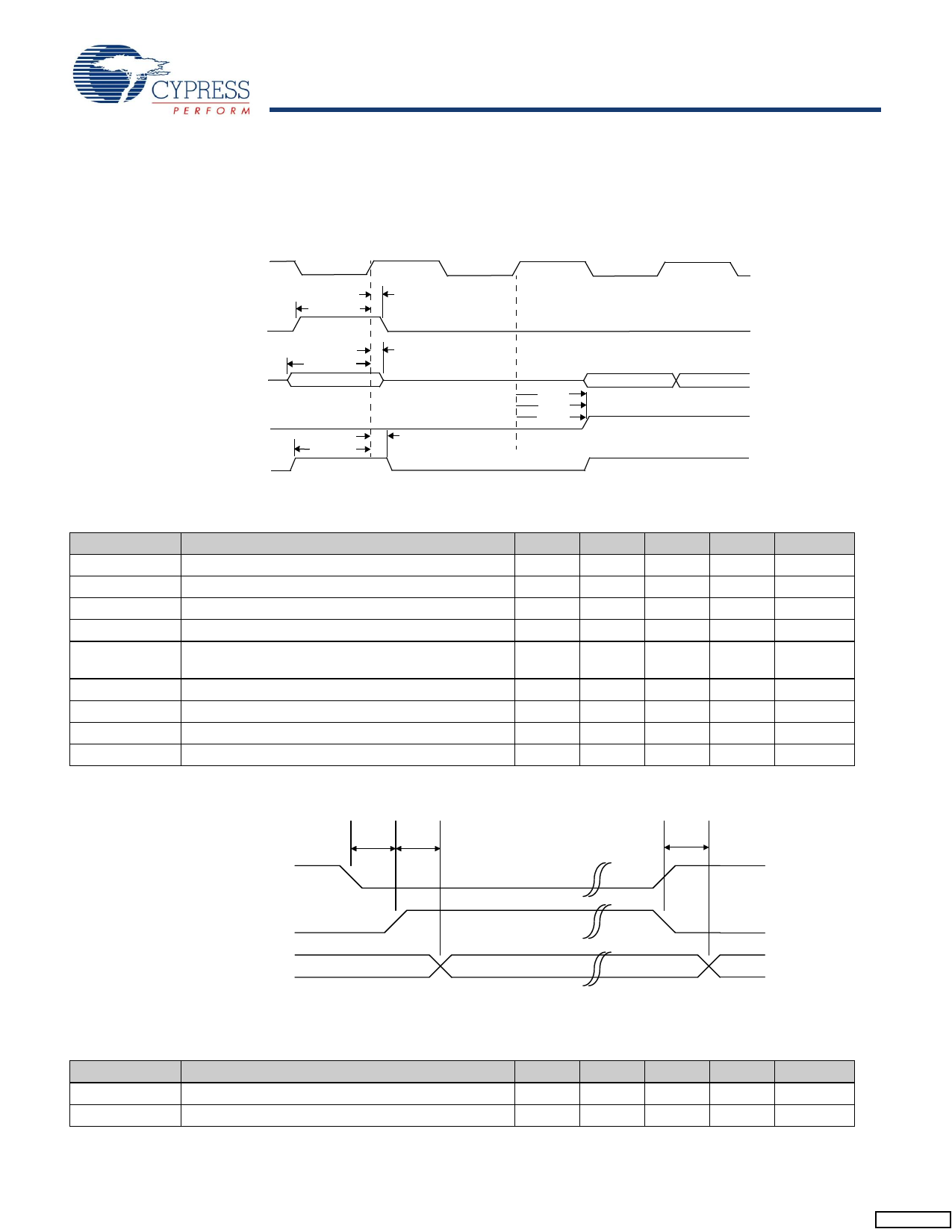

HS/FS Interface Timing - 30 MHz

Figure 4. 30 MHz Timing Interface Timing Constraints

CY7C68000A

CLK

Control_In

DataIn

Control_Out

DataOut

TCSU_MIN

TCH_MIN

TDSU_MIN

TDH_MIN

TVSU_MIN

TVH_MIN

TCDO

TCCO

TCVO

Table 4. 30 MHz Timing Interface Timing Constraints Parameters

Parameter

Description

Min

Typ

TCSU_MIN

Minimum setup time for TXValid

16

TCH_MIN

Minimum hold time for TXValid

1

TDSU_MIN

Minimum setup time for Data (Transmit direction)

16

TDH_MIN

Minimum hold time for Data (Transmit direction)

1

TCCO

Clock to Control Out time for TXReady, RXValid,

1

RXActive and RXError

TCDO

TVSU_MIN

TVH_MIN

TCVO

Clock to Data out time (Receive direction)

1

Minimum setup time for ValidH (transmit Direction)

16

Minimum hold time for ValidH (Transmit direction)

1

Clock to ValidH out time (Receive direction)

1

Suspend

Figure 5. Tri-state Mode Timing Constraints

Ttssu Ttspd

Tri-state

Output / IO

XXXX

Hi-Z

Max

Unit

ns

ns

ns

ns

20

ns

20

ns

ns

ns

20

ns

Ttspd

Notes

Table 5. Tri-state Mode Timing Constraints Parameters

Parameter

Ttssu

Ttspd

Description

Minimum setup time for Tri-state

Propagation Delay for Tri-State mode

Document #: 38-08052 Rev. *G

Min

Typ

Max

Unit

Notes

0

ns

50

ns

Page 11 of 15

[+] Feedback