CY3681 데이터 시트보기 (PDF) - Cypress Semiconductor

부품명

상세내역

제조사

CY3681 Datasheet PDF : 48 Pages

| |||

CY7C68013

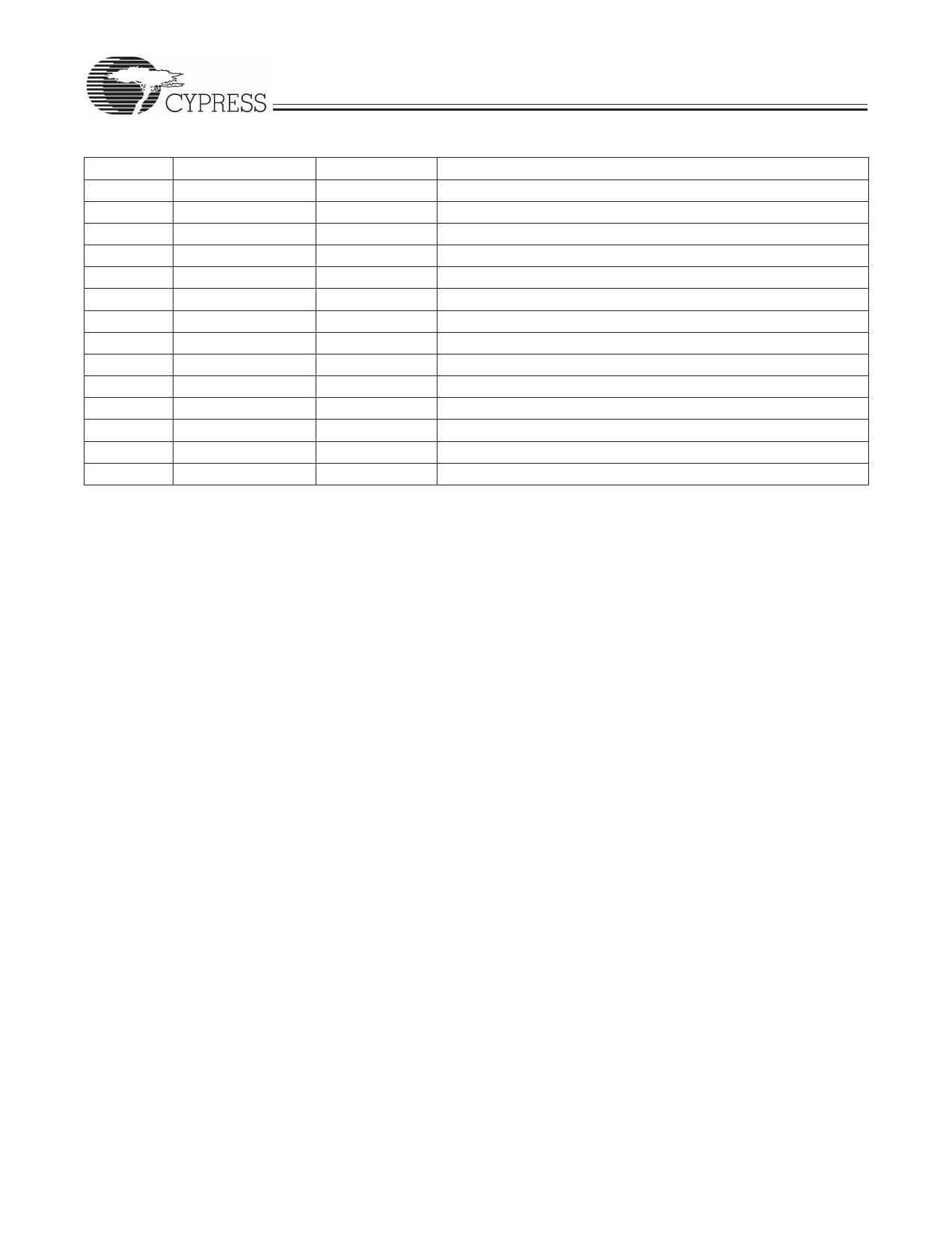

Table 3-4. Individual FIFO/GPIF Interrupt Sources

Priority

1

INT4VEC Value

80

Source

EP2PF

2

84

EP4PF

3

88

EP6PF

4

8C

EP8PF

5

90

EP2EF

6

94

EP4EF

7

98

EP6EF

8

9C

EP8EF

9

A0

EP2FF

10

A4

EP4FF

11

A8

EP6FF

12

AC

EP8FF

13

B0

GPIFDONE

14

B4

GPIFWF

Notes

Endpoint 2 Programmable Flag

Endpoint 4 Programmable Flag

Endpoint 6 Programmable Flag

Endpoint 8 Programmable Flag

Endpoint 2 Empty Flag

Endpoint 4 Empty Flag

Endpoint 6 Empty Flag

Endpoint 8 Empty Flag

Endpoint 2 Full Flag

Endpoint 4 Full Flag

Endpoint 6 Full Flag

Endpoint 8 Full Flag

GPIF Operation Complete

GPIF Waveform

3.8.3 FIFO/GPIF Interrupt (INT4)

Just as the USB Interrupt is shared among 27 individual USB-

interrupt sources, the FIFO/GPIF interrupt is shared among 14

individual FIFO/GPIF sources. The FIFO/GPIF Interrupt, like

the USB Interrupt, can employ autovectoring. Table 3-4 shows

the priority and INT4VEC values for the 14 FIFO/GPIF

interrupt sources.

If Autovectoring is enabled (AV4EN = 1 in the INTSETUP

register), the FX2 substitutes its INT4VEC byte. Therefore, if

the high byte (“page”) of a jump-table address is preloaded at

location 0x0054, the automatically-inserted INT4VEC byte at

0x0055 will direct the jump to the correct address out of the 14

addresses within the page. When the ISR occurs, the FX2

pushes the program counter onto its stack then jumps to

address 0x0053, where it expects to find a “jump” instruction

to the ISR Interrupt service routine.

3.9 Reset and Wakeup

3.9.1 Reset Pin

An input pin (RESET#) resets the chip. This pin has hysteresis

and is active LOW. The internal PLL stabilizes approximately

200 µs after VCC has reached 3.3V. Typically, an external RC

network (R = 100k, C = 0.1 µF) is used to provide the RESET#

signal.

3.9.2 Wakeup Pins

The 8051 puts itself and the rest of the chip into a power-down

mode by setting PCON.0 = 1. This stops the oscillator and

PLL. When WAKEUP is asserted by external logic, the oscil-

lator restarts and after the PLL stabilizes, and the 8051

receives a wakeup interrupt. This applies whether or not FX2

is connected to the USB.

The FX2 exits the power down (USB suspend) state using one

of the following methods:

• USB bus signals resume

• External logic asserts the WAKEUP pin

• External logic asserts the PA3/WU2 pin.

The second wakeup pin, WU2, can also be configured as a

general purpose I/O pin. This allows a simple external R-C

network to be used as a periodic wakeup source.

3.10 Program/Data RAM

3.10.1 Size

The FX2 has eight kbytes of internal program/data RAM,

where PSEN#/RD# signals are internally ORed to allow the

8051 to access it as both program and data memory. No USB

control registers appear in this space.

Two memory maps are shown in the following diagrams:

Figure 3-1 Internal Code Memory, EA = 0

Figure 3-2 External Code Memory, EA = 1.

3.10.2 Internal Code Memory, EA = 0

This mode implements the internal eight-kbyte block of RAM

(starting at 0) as combined code and data memory. When

external RAM or ROM is added, the external read and write

strobes are suppressed for memory spaces that exist inside

the chip. This allows the user to connect a 64-kbyte memory

without requiring address decodes to keep clear of internal

memory spaces.

Only the internal eight kbytes and scratch pad 0.5 kbytes

RAM spaces have the following access:

• USB download

• USB upload

• Setup data pointer

• I2C-compatible interface boot load.

3.10.3 External Code Memory, EA = 1

The bottom eight kbytes of program memory is external, and

therefore the bottom eight kbytes of internal RAM is accessible

only as data memory.

Document #: 38-08012 Rev. *E

Page 5 of 48