CY7C9235(1999) 데이터 시트보기 (PDF) - Cypress Semiconductor

부품명

상세내역

제조사

CY7C9235 Datasheet PDF : 7 Pages

| |||

PRELIMINARY

CY7C9235

Pin Descriptions

CY7C9235 SMPTE-259M Encoder

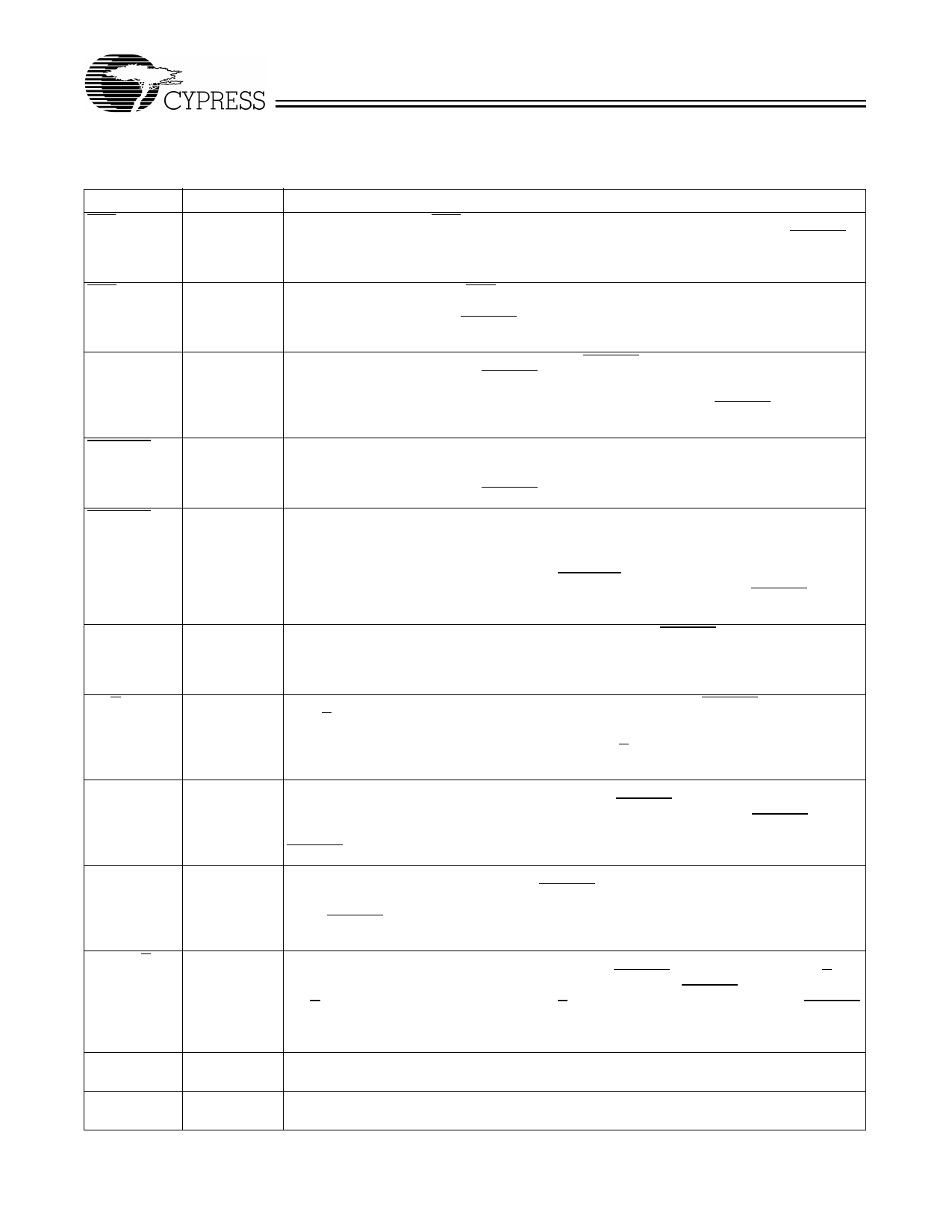

Name

ENA

I/O

Input

ENN

Input

BYPASS

Input

TRS_DET Output

TRS_FILT

Input

SVS_EN

Input

SC/D_EN

Input

PD9(SVS)

Input

PD8–1

Input

PD0(SC/D) Input

Q9(SVS)

Q8–1

Output

Output

Description

Enable Parallel Data. If ENA is LOW at the rising edge of CKW, the data present on the PD0−9

inputs is latched, and routed to the Q0–9 outputs. This pin is only interpreted when DVB_EN is

active (LOW). If the CY7C9235 is only used in SMPTE-259M mode this signal should be tied

to VSS.

Enable Next Parallel Data. If ENN is LOW at the rising edge of CKW, the data present on the

PD0–9 inputs at the next rising edge of TXCLK is latched, and routed to the Q0–9 outputs. This

pin is only interpreted when DVB_EN is active (LOW). If the CY7C9235 is only used in

SMPTE-259M mode this signal should be tied to VSS.

Bypass SMPTE Encoding. BYPASS is ignored if DVB_EN is active (LOW). If BYPASS is HIGH

at the rising edge of CKW (and DVB_EN is HIGH), the data latched into the input register is

routed around both the SMPTE scrambler and the NRZI encoder and presented to the output

register. If BYPASS is LOW at the rising edge of the CKW clock (and DVB_EN is HIGH), the

data present in the input register is routed through the SMPTE scrambler and NRZI encoder.

TRS Character Detected. This output indicates when a character used in the TRS sequence is

detected in the input register. If the data contains any of the reserved characters of 000–003 or

3FC–3FF in 10-bit hex, the output will be LOW for one clock period. If the character in the input

register is any other pattern (or DVB_EN is LOW) this output will remain HIGH.

TRS Character Filter. This signal controls an internal filter that converts the low-order two bits

of all TRS characters to same state as the upper eight bits. This allows a proper 30-bit TRS ID

to be generated when the CY7C9235 is operated with 8-bit or non-standard video streams.

When this signal is LOW, all characters from 000–003 are converted to 000, and all characters

from 3FC–3FF are converted to 3FF. When TRS_FILT is disabled (HIGH), all characters are

passed to the scrambler without modification. This signal has no effect when DVB_EN is active

(LOW).

Send Violation Symbol Enable. This input is only valid when DVB_EN is active (LOW). If

SVS_EN is HIGH and a HIGH input is present on PD9, Q9 will also be high on a following clock

cycle, forcing the CY7B9234 serializer to generate an invalid 8B/10B character. If SVS_EN is

LOW, the level present on PD9 is ignored and Q9 is forced to a LOW state.

Special Character/Data Select Enable. This input is only valid when DVB_EN is active (LOW).

If SC/D_EN is HIGH and a HIGH input is present on PD0, Q0 will also be high on a following

clock cycle, forcing the CY7B9234 serializer to generate an 8B/10B control character as select-

ed by the character present on the PD8–1 inputs. If SC/D_EN is LOW, the level present on PD0

is ignored and Q0 is forced to a LOW (data only) state.

Parallel Data 9 or Send Violation Symbol. This is the MSB of the input data field. It is latched

in the input register at the rising edge of CKW. When DVB_EN is active (LOW) and SVS_EN

is HIGH, this latched input is routed to the output register bit Q9 (SVS). When DVB_EN is active

(LOW) and SVS_EN is LOW, output register bit Q9 (SVS) is forced to a LOW (zero) level. When

DVB_EN is inactive (HIGH), this latched input is routed to the scrambler and NRZI encoder.

Parallel Data 8 through 1. The signals present at the PD8–1 inputs are latched in the input

register at the rising edge of CKW. When DVB_EN is HIGH, these signals are the middle eight

bits of the SMPTE 10-bit data field, and are then routed to the scrambler and NRZI encoder.

When DVB_EN is active (LOW), these signals are full DVB-ASI data bus, and are then routed

to the Q8−1 outputs.

Parallel Data 0 or Special Code/Data Select. This is the LSB of the input data field. It is latched

in the input register at the rising edge of CKW. When DVB_EN is active (LOW) and SC/D_EN

is HIGH, this input is routed to output register bit Q0 (SVS). When DVB_EN is active (LOW) and

SC/D_EN is LOW, output register bit Q0 (SC/D) is forced to a LOW (zero) level. When DVB_EN

is inactive (HIGH), this input data bit is routed through the input register and the scrambler and

NRZI encoder.

Output Bit 9. This is the MSB of the output register. It should be connected directly to the

CY7B9234 serializer input signal SVS(Dj).

Output Bits 8 through 1. These signals should be connected directly to the CY7B9234 serializer

input signals D7−0 respectively.

3