DS2251T(1995) 데이터 시트보기 (PDF) - Dallas Semiconductor -> Maxim Integrated

부품명

상세내역

제조사

DS2251T Datasheet PDF : 19 Pages

| |||

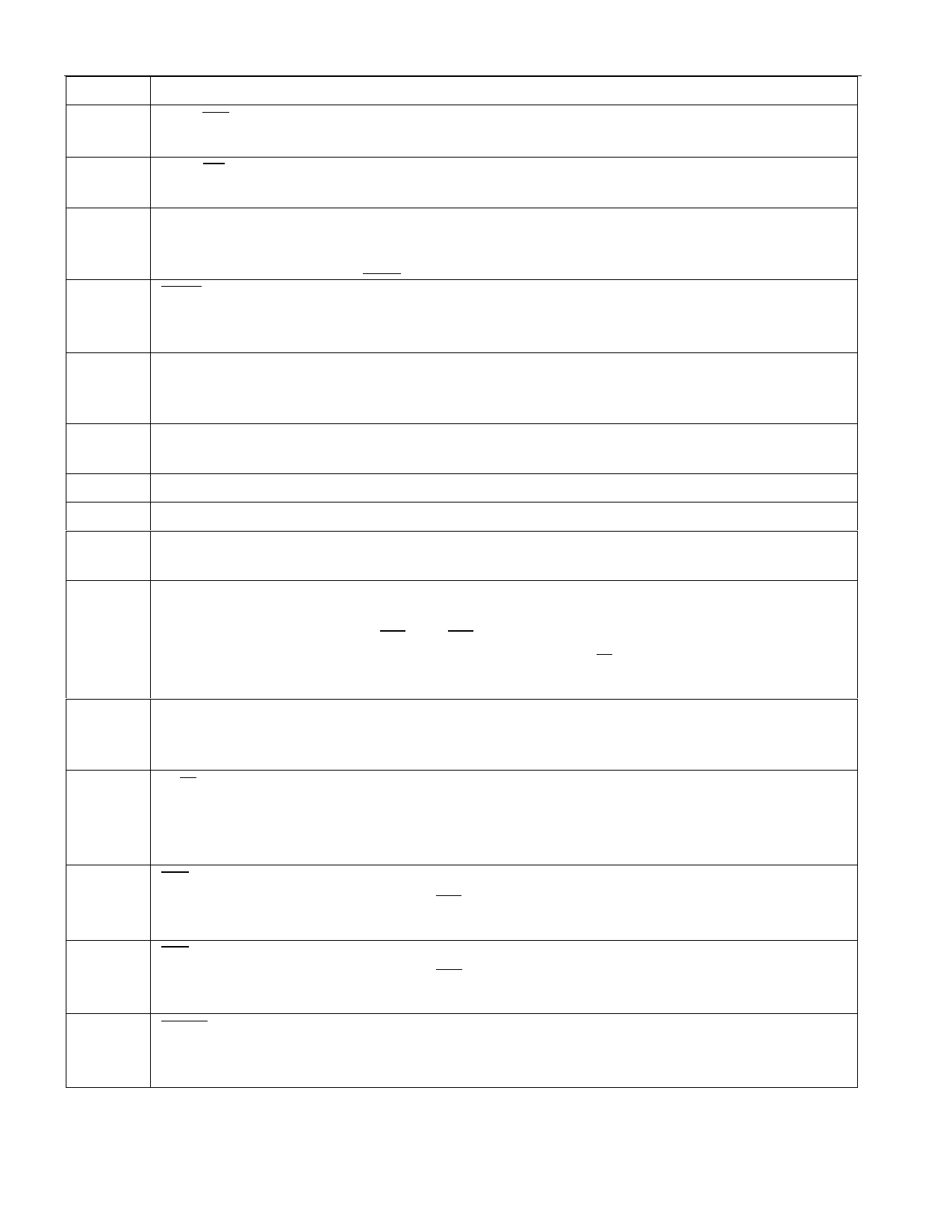

DS2251T

PIN

9

29

30

19, 18

20

40

72

54–41

63–56

64

66

67

31

71

65

55

DESCRIPTION

RST – Active high reset input. A logic 1 applied to this pin will activate a reset state. This pin

is pulled down internally, can be left unconnected if not used. An RC power–on reset circuit is

not needed and is NOT recommended.

PSEN – Program Store Enable. This active low signal is used to enable an external program

memory when using the Expanded bus. It is normally an output and should be unconnected if

not used.

ALE – Address Latch Enable. Used to de–multiplex the multiplexed Expanded Address/Data

bus on Port 0. This pin is normally connected to the clock input on a ’373 type transparent

latch.

XTAL2, XTAL1. Used to connect an external crystal to the internal oscillator. XTAL1 is the

input to an inverting amplifier and XTAL2 is the output.

GND – Logic ground.

VCC – +5V.

BA15 – Monitor test point to reflect the logical value of A15. Not needed for memory access.

BA13 – 0. Byte–wide Address bus bits 13–0. This bus is combined with the non–multiplexed

data bus (BD7–0) to access on–board NVSRAM and off–board peripherals. Peripheral

decoding is performed using PE3 and PE4. These are on 16K boundaries, so BA14 or BA15

are not needed. Read/write access is controlled by R/W. BA13–0 connect directly to memory

mapped peripherals.

BD7 – 0. Byte–wide Data bus bits 7–0. This 8 bit bi–directional bus is combined with the

non–multiplexed address bus (BA14–0) to access on–board NVSRAM and off–board periph-

erals.

R/W – Read/Write. This signal provides the write enable to the SRAMs on the Byte–wide bus.

It is controlled by the memory map and Partition. The blocks selected as Program (ROM) will

be write protected. This signal is also used for the write enable to off–board peripherals.

PE3 – Peripheral Enable 3. Accesses data memory between addresses 8000h and BFFFh

when the PES bit is set to a logic 1. PE3 is not lithium backed and can be connected to any

type of peripheral function.

PE4 – Peripheral Enable 4. Accesses data memory between addresses C000h and FFFFh

when the PES bit is set to a logic 1. PE4 is not lithium backed and can be connected to any

type of peripheral function.

PROG – Invokes the Bootstrap loader on a falling edge. This signal should be debounced so

that only one edge is detected. If connected to ground, the micro will enter Bootstrap loading

on power up. This signal is pulled up internally.

VRST – This I/O pin indicates that the power supply (VCC) has fallen below the VCCMIN level

and the micro is in a reset state. When this occurs, the DS2251T will drive this pin to a logic

0. Because the micro is lithium backed, this signal is guaranteed even when VCC=0V.

Because it is an I/O pin, it will also force a reset if pulled low externally. This allows multiple

parts to synchronize their power–down resets.

PF – This output goes to a logic 0 to indicate that the micro has switched to lithium backup. It

corresponds to VCC < VLI. Because the micro is lithium backed, this signal is guaranteed

even when VCC=0V.

INTB – INTB from the real time clock. This output may be connected to a micro interrupt

input.

121395 5/19