HM6264BLP 데이터 시트보기 (PDF) - Hitachi -> Renesas Electronics

부품명

상세내역

제조사

HM6264BLP Datasheet PDF : 15 Pages

| |||

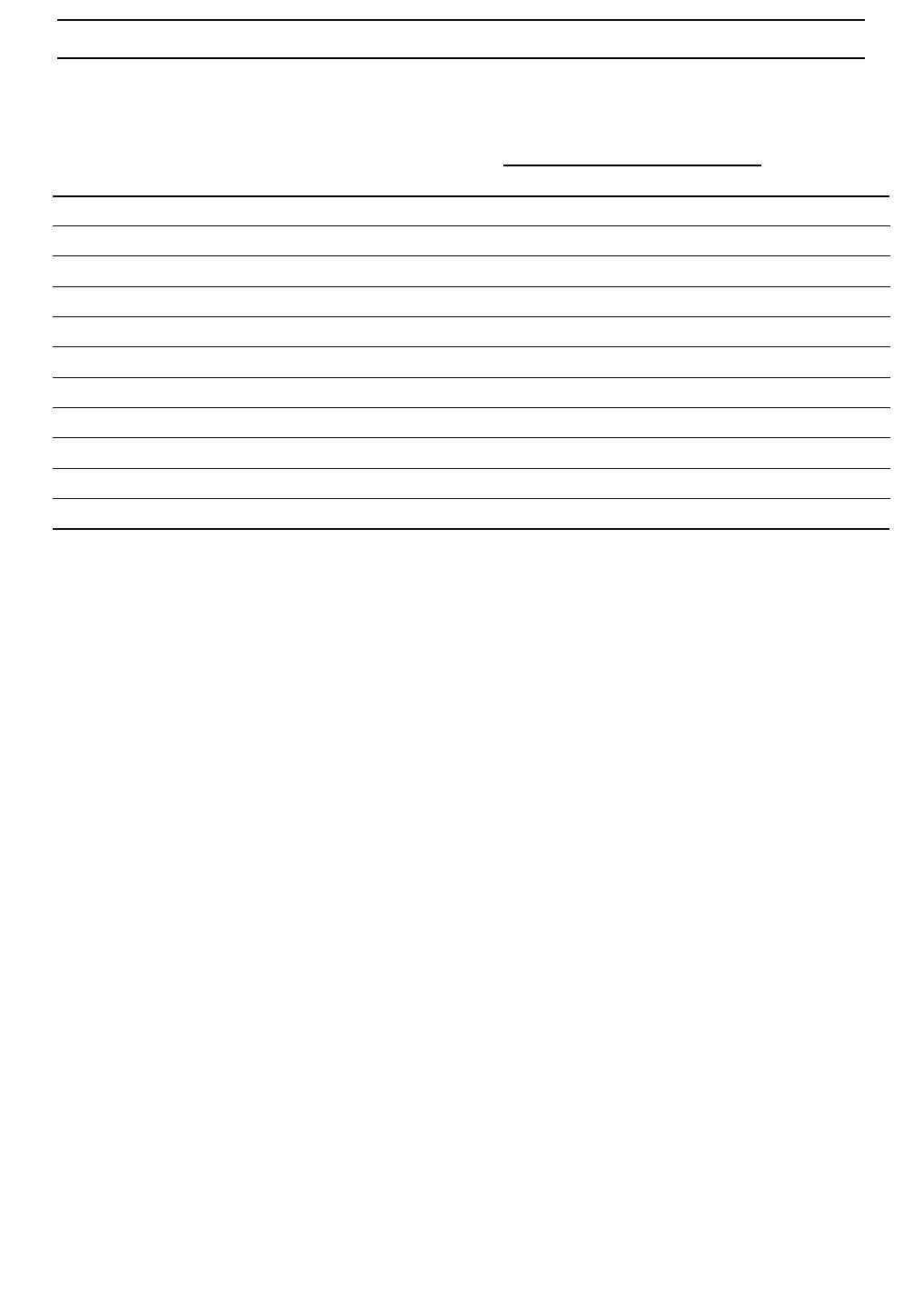

HM6264B Series

Write Cycle

HM6264B-8L HM6264B-10L

Parameter

Symbol Min Max Min Max Unit Notes

Write cycle time

t WC

85

—

100 —

ns

Chip selection to end of write

t CW

75

—

80

—

ns

2

Address setup time

t AS

0

—

0

—

ns

3

Address valid to end of write

t AW

75

—

80

—

ns

Write pulse width

t WP

55

—

60

—

ns

1, 6

Write recovery time

t WR

0

—

0

—

ns

4

WE to output in high-Z

t WHZ

0

30

0

35

ns

5

Data to write time overlap

t DW

40

—

40

—

ns

Data hold from write time

t DH

0

—

0

—

ns

Output active from end of write

t OW

5

—

5

—

ns

Output disable to output in high-Z

t OHZ

0

30

0

35

ns

5

Notes: 1. A write occurs during the overlap of a low CS1, and high CS2, and a high WE. A write begins

at the latest transition among CS1 going low,CS2 going high and WE going low. A write ends

at the earliest transition among CS1 going high CS2 going low and WE going high. Time tWP is

measured from the beginning of write to the end of write.

2. tCW is measured from the later of CS1 going low or CS2 going high to the end of write.

3. tAS is measured from the address valid to the beginning of write.

4. tWR is measured from the earliest of CS1 or WE going high or CS2 going low to the end of write

cycle.

5. During this period, I/O pins are in the output state, therefore the input signals of the opposite

phase to the outputs must not be applied.

6. In the write cycle with OE low fixed, tWP must satisfy the following equation to avoid a problem

of data bus contention

tWP ≥ tWHZ max + tDW min.