HT46C23 데이터 시트보기 (PDF) - Holtek Semiconductor

부품명

상세내역

제조사

HT46C23 Datasheet PDF : 48 Pages

| |||

HT46R23/HT46C23

The internal timer/event counter interrupt is initialized by

setting the timer/event counter interrupt request flag

(TF; bit 5 of INTC0), caused by a timer overflow. When

the interrupt is enabled, the stack is not full and the TF

bit is set, a subroutine call to location 08H will occur. The

related interrupt request flag (TF) will be reset and the

EMI bit cleared to disable further interrupts.

The A/D converter interrupt is initialized by setting the

A/D converter request flag (ADF; bit 6 of INTC0),

caused by an end of A/D conversion. When the interrupt

is enabled, the stack is not full and the ADF is set, a sub-

routine call to location 0CH will occur. The related inter-

rupt request flag (ADF) will be reset and the EMI bit

cleared to disable further interrupts.

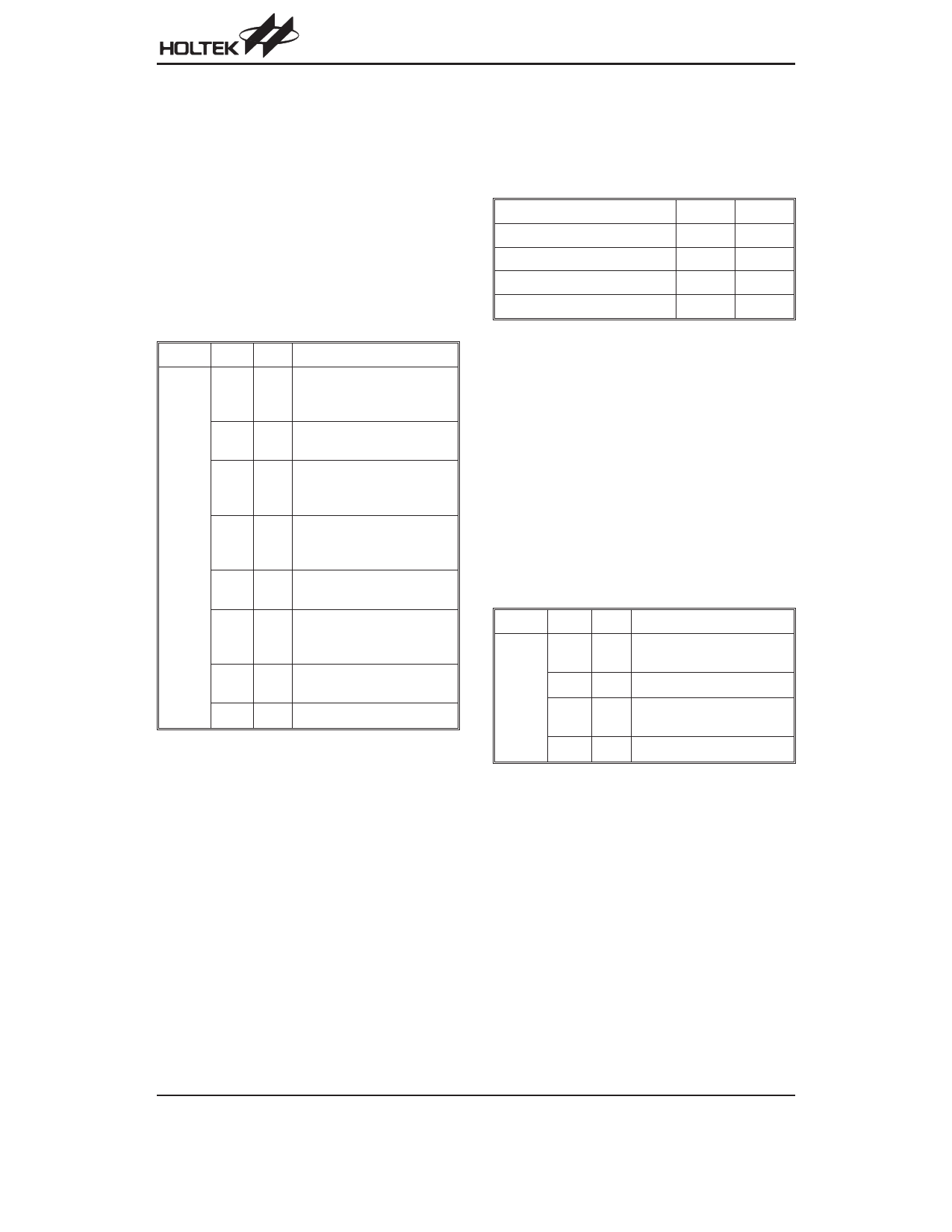

Register Bit No. Label

Function

Controls the master (global)

0 EMI interrupt

(1=enabled; 0=disabled)

1

EEI

Controls the external interrupt

(1=enabled; 0=disabled)

Controls the timer/event

2 ETI counter interrupt

(1=enabled; 0=disabled)

INTC0

(0BH)

Controls the A/D converter

3 EADI interrupt

(1=enabled; 0=disabled)

4

EIF

External interrupt request flag

(1=active; 0=inactive)

Internal timer/event counter

5 TF request flag

(1=active; 0=inactive)

6

ADF

A/D converter request flag

(1=active; 0=inactive)

7 ¾ Unused bit, read as ²0²

INTC0 Register

The I2C Bus interrupt is initialized by setting the I2C Bus

interrupt request flag (HIF; bit 4 of INTC1), caused by a

slave address match (HAAS=²1²) or one byte of data trans-

fer is completed. When the interrupt is enabled, the stack

is not full and the HIF bit is set, a subroutine call to location

10H will occur. The related interrupt request flag (HIF) will

be reset and the EMI bit cleared to disable further inter-

rupts.

During the execution of an interrupt subroutine, other in-

terrupt acknowledgments are held until the ²RETI² in-

struction is executed or the EMI bit and the related

interrupt control bit are set to 1 (of course, if the stack is

not full). To return from the interrupt subroutine, ²RET² or

²RETI² may be invoked. RETI will set the EMI bit to en-

able an interrupt service, but RET will not.

Interrupts, occurring in the interval between the rising

edges of two consecutive T2 pulses, will be serviced on

the latter of the two T2 pulses, if the corresponding inter-

rupts are enabled. In the case of simultaneous requests

the following table shows the priority that is applied.

These can be masked by resetting the EMI bit.

Interrupt Source

External Interrupt

Timer/Event Counter Overflow

A/D Converter Interrupt

Serial bus interrupt

Priority

1

2

3

4

Vector

04H

08H

0CH

10H

The timer/event counter interrupt request flag (TF), ex-

ternal interrupt request flag (EIF), A/D converter request

flag (ADF), the I2C Bus interrupt request flag (HIF), en-

able timer/event counter bit (ETI), enable external inter-

rupt bit (EEI), enable A/D converter interrupt bit (EADI),

enable I2C Bus interrupt bit (EHI) and enable master in-

terrupt bit (EMI) constitute an interrupt control register 0

(INTC0) and an interrupt control register 1 (INTC1)

which are located at 0BH and 1EH in the data memory.

EMI, EEI, ETI, EADI, EHI are used to control the en-

abling/disabling of interrupts. These bits prevent the re-

quested interrupt from being serviced. Once the

interrupt request flags (TF, EIF, ADF, HIF) are set, they

will remain in the INTC0 and INTC1 register until the in-

terrupts are serviced or cleared by a software instruc-

tion.

Register Bit No. Label

Function

0

EHI

Controls the I2C Bus interrupt

(1= enabled; 0= disabled)

INTC1 1~3 ¾ Unused bit, read as ²0²

(1EH)

4

HIF

I2C Bus interrupt request flag

(1= active; 0= inactive)

5~7 ¾ Unused bit, read as ²0²

INTC1 Register

It is recommended that a program does not use the

²CALL subroutine² within the interrupt subroutine. In-

terrupts often occur in an unpredictable manner or

need to be serviced immediately in some applications.

If only one stack is left and enabling the interrupt is not

well controlled, the original control sequence will be dam-

aged once the ²CALL² operates in the interrupt subrou-

tine.

Rev. 1.60

10

May 3, 2004