HT82V36 데이터 시트보기 (PDF) - Holtek Semiconductor

부품명

상세내역

제조사

HT82V36 Datasheet PDF : 10 Pages

| |||

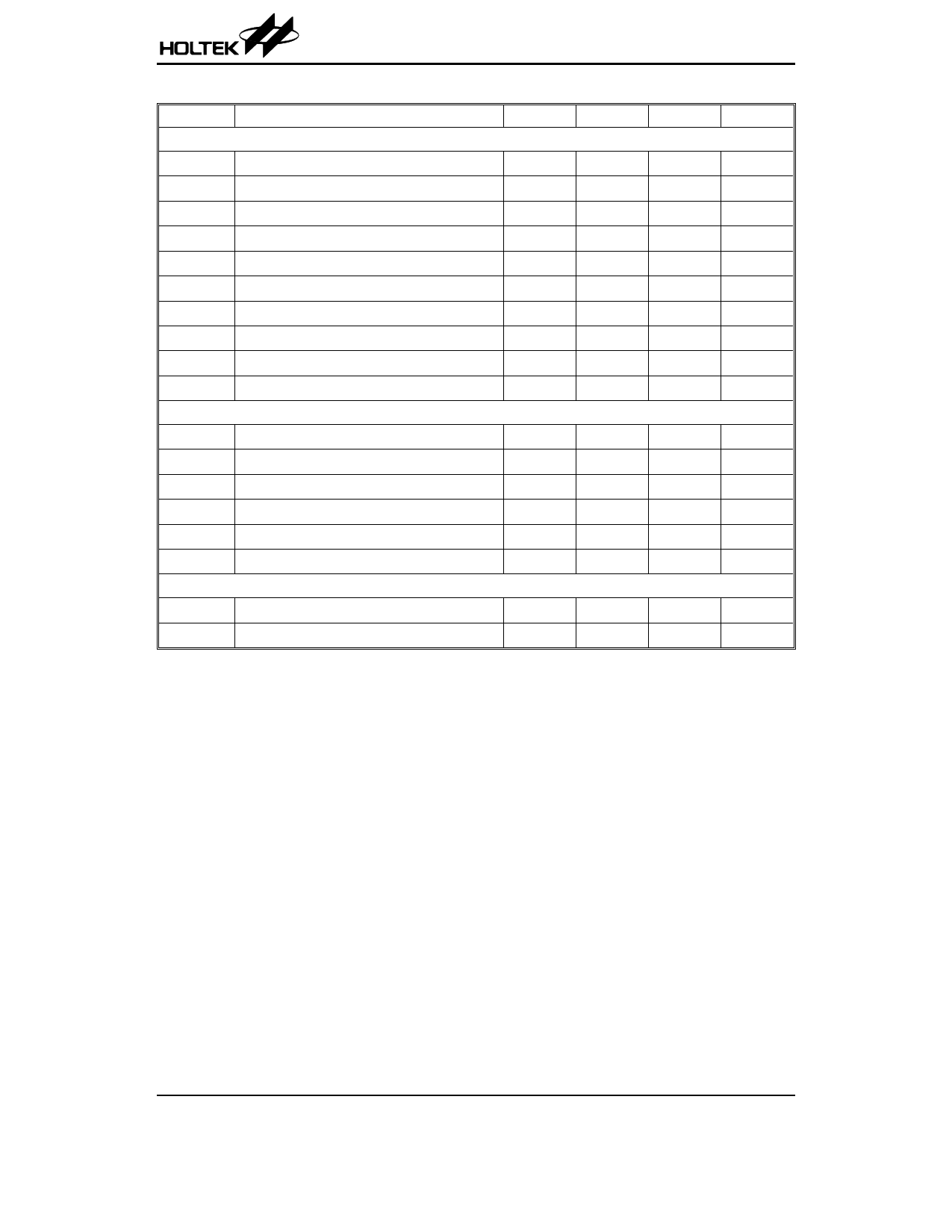

Timing Specification

Symbol

Parameter

Clock Parameters

tADCLK

Pixel Rate Clock

tADH

ADCCLK Pulse High Width

tADL

ADCCLK Pulse Low Width

tC1

CDSCLK1 Pulse Width

tC2

CDS Mode CDSCLK2 Pulse Width

tC3

SHA Mode CDSCLK2 Pulse Width

tC2ADF

CDSCLK2 Falling to ADCCLK Falling

tADFC1

ADCCLK Falling to CDSCLK1 Rising

tADFC2

ADCCLK Falling to CDSCLK2 Rising

tAD

Analog Sampling Delay

Serial Interface

fSCLK

Maximum SCLK Frequency

tLS

SLOAD to SCLK Setup Time

tLH

SCLK to SLOAD Hold Time

tDS

SDATA to SCLK Rising Setup Time

tDH

SCLK Rising to SDATA Hold Time

tRDV

Falling to SDATA Valid

Data Output

tOD

Output Delay

Latency (Pipeline Delay)

HT82V36

Min.

166

80

80

20

20

40

60

2

2

5

10

10

10

10

10

10

¾

¾

Typ.

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

¾

8

9

Max.

Unit

¾

ns

ns

ns

¾

ns

¾

ns

¾

ns

¾

ns

¾

ns

¾

ns

¾

ns

¾

MHz

¾

ns

¾

ns

¾

ns

¾

ns

¾

ns

¾

ns

¾

Cycles

Functional Description

Integral Nonlinear (INL)

Integral nonlinear error refers to the deviation of each in-

dividual code from a line drawn from zero scale through

positive full scale. The point used as zero scale occurs 1

/2 LSB before the first code transition. Positive full scale

is defined as a level 1/2 LSB beyond the last code transi-

tion. The deviation is measured from the middle of each

particular code to the true straight line.

Differential Nonlinear (DNL)

An ideal ADC exhibits code transitions that are exactly 1

LSB apart. DNL is the deviation from this ideal value.

Thus every code must have a finite width. No missing

codes guaranteed to 16-bit resolution indicates that all

4096 codes, respectively, must be present over all oper-

ating ranges.

Offset Error

The first ADC code transition should occur at a level 1/2

LSB above the nominal zero scale voltage.

The offset error is the deviation of the actual first code

transition level from the ideal level.

Gain Error

The last code transition should occur for an analog

value 1/2 LSB below the nominal full-scale voltage.

Gain error is the deviation of the actual difference be-

tween first and last code transitions and the ideal differ-

ence between the first and last code transitions.

Aperture Delay

The aperture delay is the time delay that occurs when a

sampling edge is applied to the HT82V36 until the actual

sample of the input signal is held. Both CDSCLK1 and

CDSCLK2 sample the input signal during the transition

from high to low, so the aperture delay is measured from

each clock¢s falling edge to the instant the actual inter-

nal sample is taken.

Rev. 1.30

4

June 29, 2004